Other Parts Discussed in Thread: C2000WARE, DP83620, DP83640

Hello Guys,

Good day.

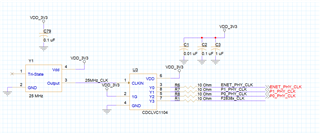

Our customer have a question about the F28388DZWTS. He saw the errata about using a gigabit phy for the ethercat. He used the DP83867IRPAPT. He also used this for the ethernet. He saw that the F28388 does not support gigabit ethernet. Can you still use the DP83867 in 10/100 mode with the F28388?

Thanks and regards,

Art