Other Parts Discussed in Thread: UC3854, UC1854

Hi Experts,

Good day. Seeking your assistance on this query from a customer:

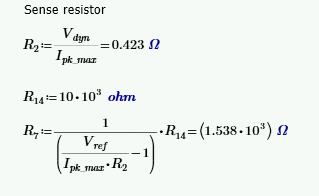

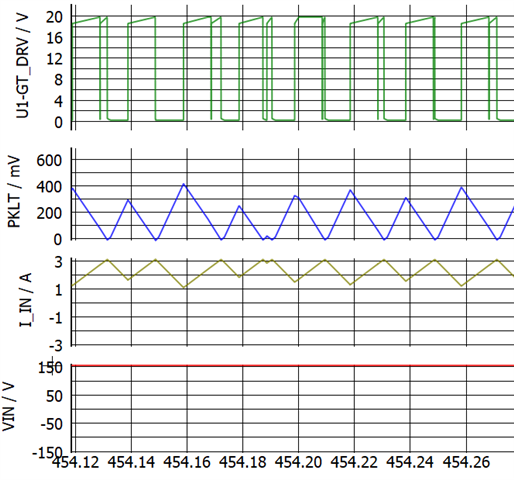

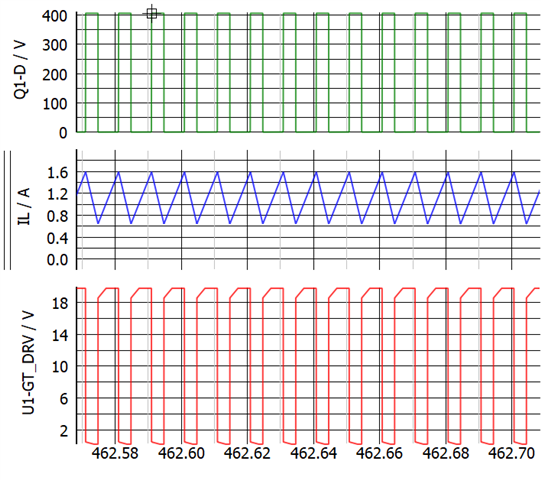

"I have a PFC boost converter design based on the data sheet of this chip. It is a 150W power supply with universal input of 85Vac-264Vac.

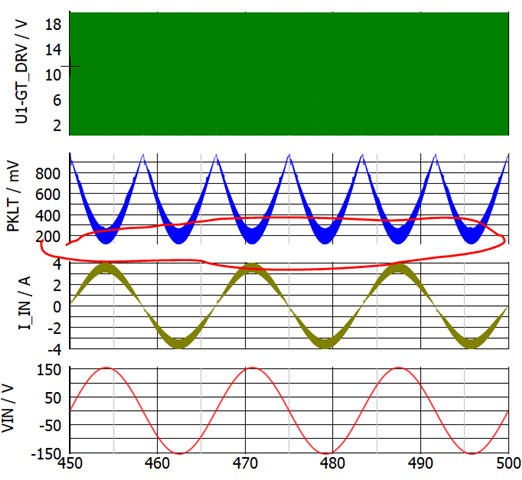

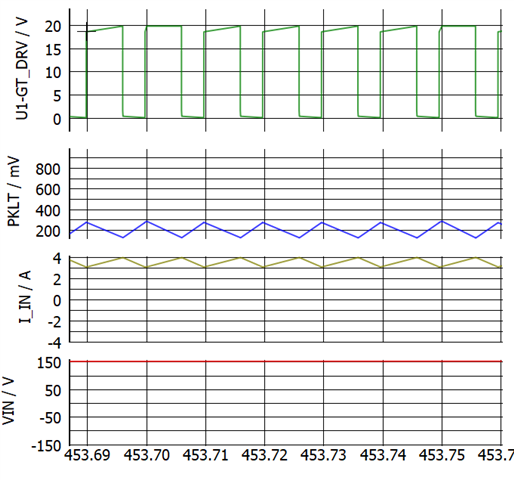

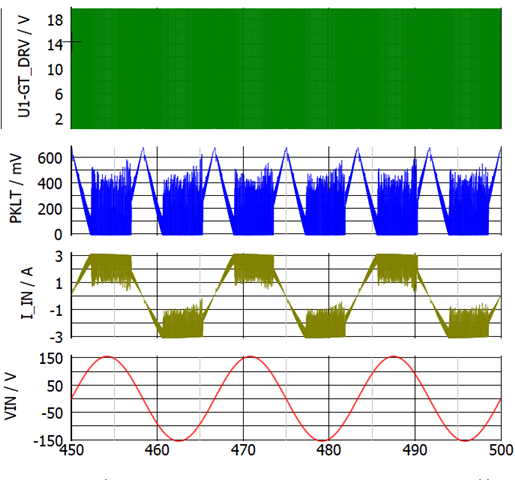

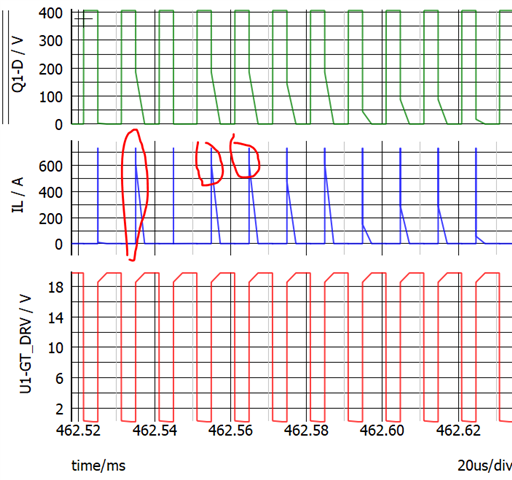

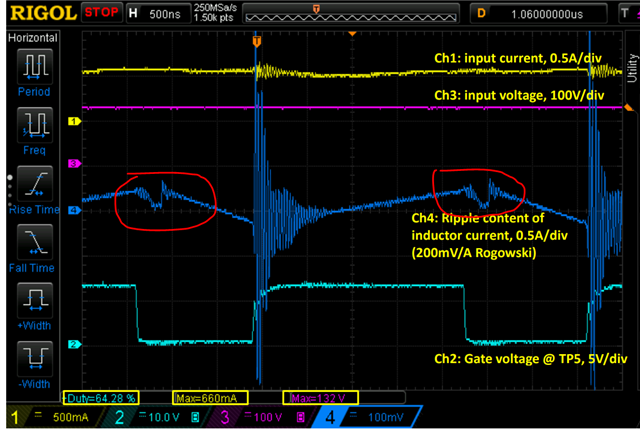

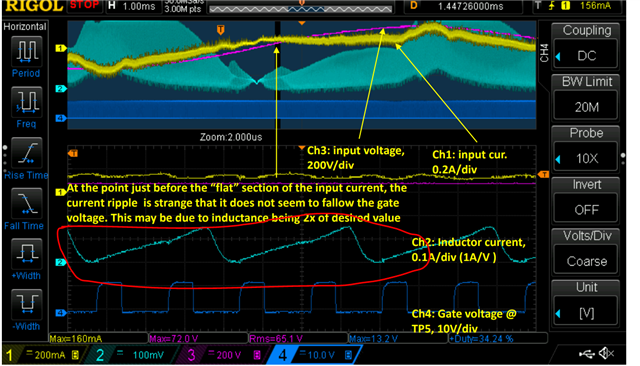

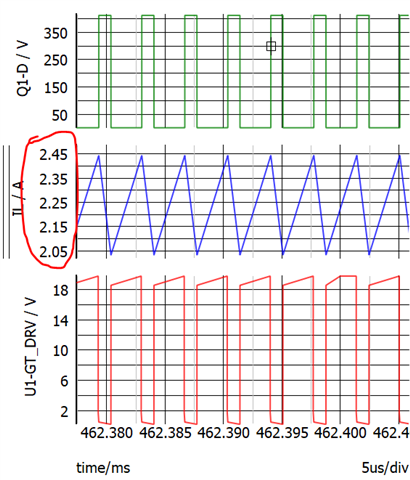

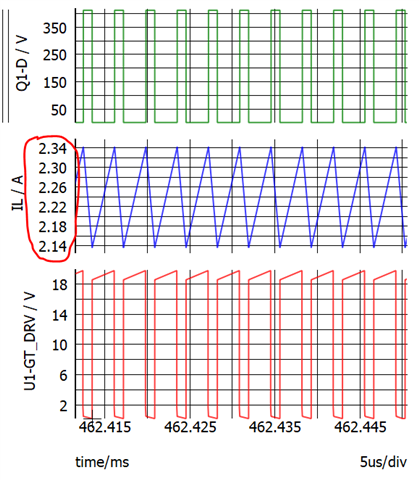

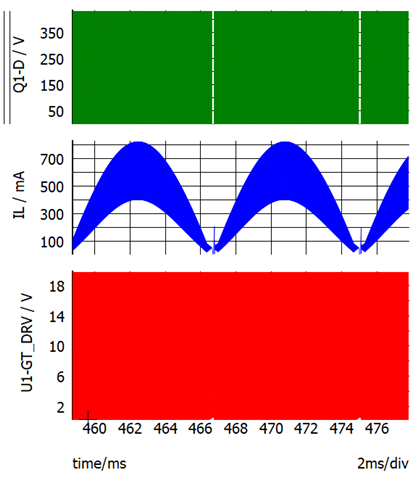

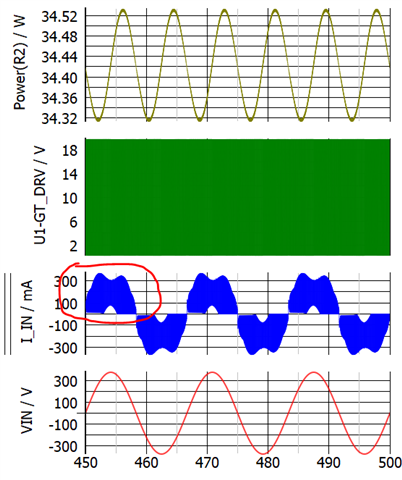

The PFC function is lost above 220Vac; I am trying to identify what may cause that.

Not damaged but my duty cycle becomes so small at the peaks of input voltage that i get significant distortions in the current waveform."

Customer have done fair amount of investigation on the problem and wanted to give a complete description of the design, problem encountered, and steps taken to mitigate it.

I have attached the files shared/summarized by the customer about the two queries.

Looking forward to hearing your support. Thank you.

Regards,

Archie A.