Other Parts Discussed in Thread: TIDA-010030

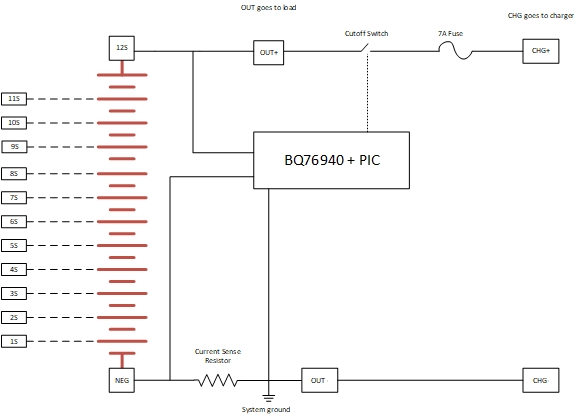

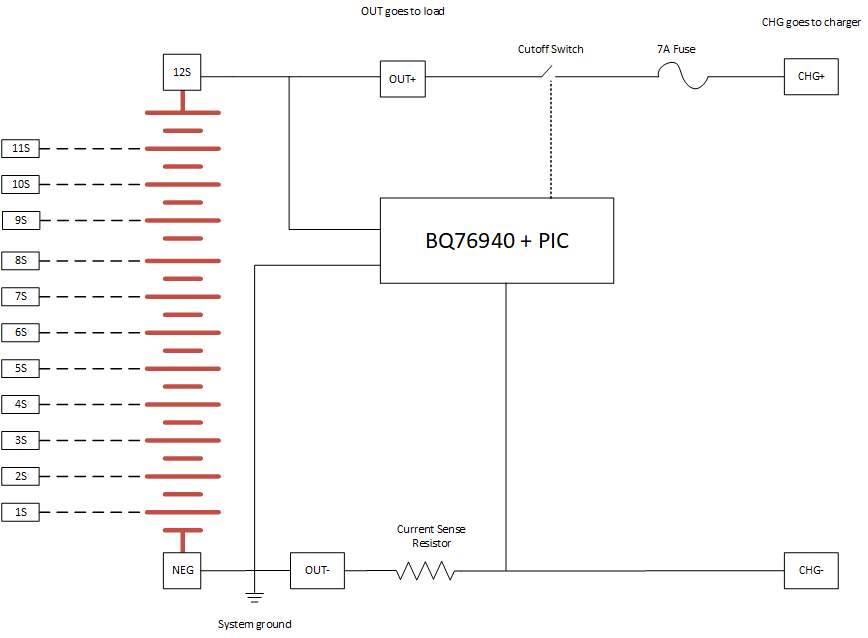

I have finished my BQ76940 schematic (attached). I'm attaching a block diagram that may help show what I'm trying to do. I followed the Top 10 Design Considerations, TIDA-010030, and the schematic video.

I decided to use the current sense circuit. I've connected the current sense pins in a way that makes sense to me. Can you check if I have it connected OK? I think in the top 10 design considerations doc it allows what I'm trying to do, but do I need shotkeys on either side of the current sense resistor for protection?

Also, since I'm not using CHG/DSG pins, do I really need to make use of the ALERT pin? I have a dedicated micro, can I just poll the status registers?

I'm using external N-channel balancing, 20mA. I put a TVS diode across each cell because the battery connections will be made with a welder. I've simulated the balance circuit in LTspice and it works well. I found the MOSFET Vgs_th(max) needs to be low...

And finally, can you check the voltage ratings on the caps I have selected?

Any other suggestions before I start layout? I think I still need to add a TVS at the top of the pack and at the charger input.

Thanks!

Erik