Other Parts Discussed in Thread: UCC27324

SIRS,

I AM IN NEED OF YOUR EXPERT WAVEFORM DIAGNOSTIC SKILLS. THE PROJECT I AM WORKING ON USES THE UCC28950 IC.ALL MY OUTPUT SIGNALS, IN MY OPINION, LOOK ABOVE AVERAGE. HERE IS A QUICKVIEW OF MAJOR COMPONENTS USED:

PSFB IC: UCC280950 (fsw:100KHz)

GATE DRIVE TRANSFORMER: COILCRAFT SD250-3L (double-ended)

DC LINK VOLTAGE: 400VDC <2% ripple

MOSFET: IPW60R170CFD7XKS (650V, IDpulse 51A)

Power Transformer: Ratio 12:1, Lmag: 1mH, Llk: 14.22uH

Gate Voltage: 8.5VDC

Watts (max): 1,250 watts

LS not used -- LS -13.32uH - Calculated Ls is Negative and Ls Might Not be Needed

Now, the problem, which I see as a problem.

**PIC#1 : Q2 DRAIN WAVEFORM no load. GOOD DRAIN SIGNAL.

**PIC#2 : YELLOW, Q1 Q2 ACTIVE LEG, no Transformer Secondary load

TEAL, Q3 Q4 PASSIVE LEG, no Transformer Secondary load

GREAT SIGNAL, NO LOAD YET.

WORRIED ABOUT THE AMOUNT OF DELAY TIME

**PIC#3 : PT1 TRANS INPUT (YEL out AB fall, teal out CD rise) @100ns no load

ZOOMED IN TO 100ns FOR BETTER LOOK

I AM NOT SURE THIS IS A GOOD DELAY

WORRIED ABOUT THE AMOUNT OF DELAY TIME

PIC#4 -- PT1 TRANS INPUT (YEL out AB rise, teal out CD fall) @100ns no load

ZOOMED IN TO 100ns FOR BETTER LOOK

I AM NOT SURE THIS IS A GOOD DELAY

REALLY WORRIED ABOUT THE AMOUNT OF DELAY TIME

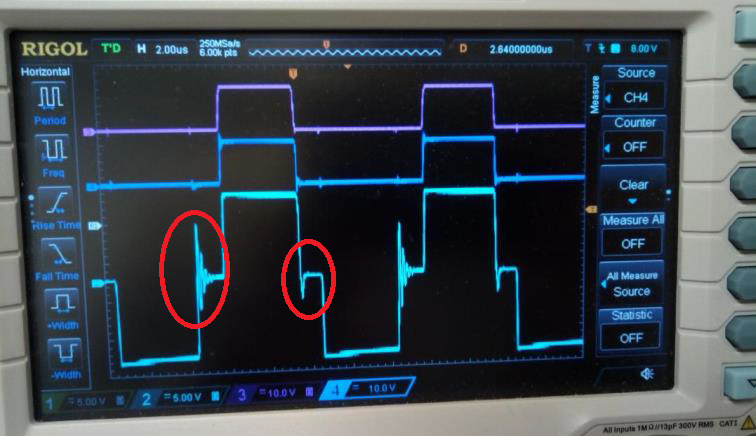

PIC#6, #7, #8 -- Now a load has been applied to the transformer secondary output winding. PIC#6 with 1.2 A resistive Load, PIC#7 with 2.4A resistive Load and PIC#8 with 3.6A resistive Load.

Notice how the waveform changes only when the load is applied. Notice also that the waveform only changes on the passive leg at positive rail and the active at negative rail. Notice that as load is increased, the waveform appears to be dividing. I say dividing because the last current test, which I was not able to record, DID DIVIDE. It actually divided into two complete side by side signals. I immediately shut the system down therefore, that is why I did not get a waveform pic.

QUESTION 1: AS EXPLAINED ABOVE REGARDING PIC#6, #7and #8, I AM LOST. I HAVE EXHAUSTED YOUR FORUM REGARDING THESE SIGNALS. PLEASE DIAGNOSE THE PROBLEM WITH THE WAVEFORMS AND LET ME KNOW YOUR IDEAS AND SUGGESTIONS.

QUESTION 2: PIC#3 and PIC#4 REGARDING THE DELAY TIME. PLEASE REVIEW THE WAVEFORMS AND LET ME KNOW ANY CONCERNS/SUGGESTIONS.

EDDIE LOY

see attached waveforms in the link below: