Hello

I am designing a board with 66AK2G12ABYA100E, in EVM schematics DDR CLK is fed from CDCM 100Mhz lvds signals, and soc datasheet tells DDR clock range of 24,25Mhz

what is the DDR clock to be fed to soc, and can we use the DDR clock generated internally of soc from SYSOSC CLK from crystal externally.

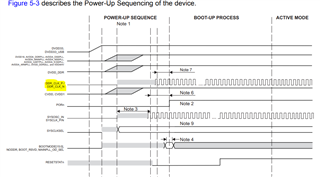

in the power-on sequence of processor attached in the image, the highlighted DDR_CLK_P and DDR_CLK_N should follow the sequence if the DDR CLK is generated internally from SYSOSC CLK fromcrystal or no?

Please guide me with ddr clocking