Part Number: AM6442

Hello TI's expert,

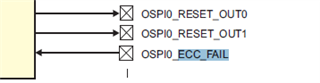

On the EVM the SoC pin E24 (OSPI0_CSn3) connect to INT# of OSPI-NOR chip.

And I read the OSPI Interrupt Requests of AM64x TRM

The OSPI module generates three interrupts. The ECC interrupts

(FSS0_OSPI_0_OSPI_ECC_CORR_LVL_INTR_0 and FSS0_OSPI_0_OSPI_ECC_UNCORR_LVL_INTR_0)

are generated by the OSPI ECC aggregator.

The other interrupt (FSS0_OSPI_0_OSPI_LVL_INTR_0) is generated by the OSPI module.

So, I mean that the OSPI0_CSn3 is configured to connect to OSPI0_ECC_FAIL to support Flash memory internal ECC.

But I saw the dts does not config pin for ECC_FAIL:

ospi0_pins_default: ospi0-pins-default {

pinctrl-single,pins = <

AM64X_IOPAD(0x0000, PIN_OUTPUT, 0) /* (N20) OSPI0_CLK */

AM64X_IOPAD(0x002c, PIN_OUTPUT, 0) /* (L19) OSPI0_CSn0 */

AM64X_IOPAD(0x000c, PIN_INPUT, 0) /* (M19) OSPI0_D0 */

AM64X_IOPAD(0x0010, PIN_INPUT, 0) /* (M18) OSPI0_D1 */

AM64X_IOPAD(0x0014, PIN_INPUT, 0) /* (M20) OSPI0_D2 */

AM64X_IOPAD(0x0018, PIN_INPUT, 0) /* (M21) OSPI0_D3 */

AM64X_IOPAD(0x001c, PIN_INPUT, 0) /* (P21) OSPI0_D4 */

AM64X_IOPAD(0x0020, PIN_INPUT, 0) /* (P20) OSPI0_D5 */

AM64X_IOPAD(0x0024, PIN_INPUT, 0) /* (N18) OSPI0_D6 */

AM64X_IOPAD(0x0028, PIN_INPUT, 0) /* (M17) OSPI0_D7 */

AM64X_IOPAD(0x0008, PIN_INPUT, 0) /* (N19) OSPI0_DQS */

>;

};

I would like to ask you how the FSS manage the ECC of OSPI device. I did not see any source code mentioned the ECC Status Register of SPI-NOR in both U-BOOT and Kernel.??

Where is irq of OSPI? I want to check if the ospi interrupt service is already check OSPI_ECC_CORR_LVL_INTR_0 or not.

I want to check the ECC of OSPI device on the Linux, How can I do it?

Many thank you for your supports

Brian.