- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello TI's expert,

On the EVM the SoC pin E24 (OSPI0_CSn3) connect to INT# of OSPI-NOR chip.

And I read the OSPI Interrupt Requests of AM64x TRM

The OSPI module generates three interrupts. The ECC interrupts

(FSS0_OSPI_0_OSPI_ECC_CORR_LVL_INTR_0 and FSS0_OSPI_0_OSPI_ECC_UNCORR_LVL_INTR_0)

are generated by the OSPI ECC aggregator.

The other interrupt (FSS0_OSPI_0_OSPI_LVL_INTR_0) is generated by the OSPI module.

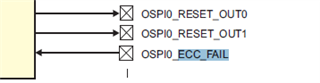

So, I mean that the OSPI0_CSn3 is configured to connect to OSPI0_ECC_FAIL to support Flash memory internal ECC.

But I saw the dts does not config pin for ECC_FAIL:

ospi0_pins_default: ospi0-pins-default {

pinctrl-single,pins = <

AM64X_IOPAD(0x0000, PIN_OUTPUT, 0) /* (N20) OSPI0_CLK */

AM64X_IOPAD(0x002c, PIN_OUTPUT, 0) /* (L19) OSPI0_CSn0 */

AM64X_IOPAD(0x000c, PIN_INPUT, 0) /* (M19) OSPI0_D0 */

AM64X_IOPAD(0x0010, PIN_INPUT, 0) /* (M18) OSPI0_D1 */

AM64X_IOPAD(0x0014, PIN_INPUT, 0) /* (M20) OSPI0_D2 */

AM64X_IOPAD(0x0018, PIN_INPUT, 0) /* (M21) OSPI0_D3 */

AM64X_IOPAD(0x001c, PIN_INPUT, 0) /* (P21) OSPI0_D4 */

AM64X_IOPAD(0x0020, PIN_INPUT, 0) /* (P20) OSPI0_D5 */

AM64X_IOPAD(0x0024, PIN_INPUT, 0) /* (N18) OSPI0_D6 */

AM64X_IOPAD(0x0028, PIN_INPUT, 0) /* (M17) OSPI0_D7 */

AM64X_IOPAD(0x0008, PIN_INPUT, 0) /* (N19) OSPI0_DQS */

>;

};I would like to ask you how the FSS manage the ECC of OSPI device. I did not see any source code mentioned the ECC Status Register of SPI-NOR in both U-BOOT and Kernel.??

Where is irq of OSPI? I want to check if the ospi interrupt service is already check OSPI_ECC_CORR_LVL_INTR_0 or not.

I want to check the ECC of OSPI device on the Linux, How can I do it?

Many thank you for your supports

Brian.

Hey Thinh,

Thank you for your question, my name is Andrew and I would be happy to assist with this. I have relayed your question to the team and hope to have a response for you within the next 1-2 business days. While I look into this, has there been any updates/developments to this problem on your end that we should take into consideration?

Best regards,

Andrew

Hey Thinh,

Thank you for your patience, the team asked me to refer you to the following E2E thread, that extensively covers the boot of Linux from OSPI on the AM64x, as well as the ECC implemented on this device: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1018036/am6442-how-to-create-ospi-rootfs-ubifs-and-boot-linux-from-ospi-without-sd

Could you please review this resource, and let me know if the answers posted to this thread provide any clarity to the problem you are facing?

Best regards,

Andrew

Hello Andrew,

This is an E2E thread created by me bout HOW TO CREATE UBI FOR ospi-rootfs. There mentions the parameter "minimum I/O unit sizes, e.g. 16 or 32 bytes in the case of ECC'd NOR flashes". I do not understand how to determine 16 or 32 so need Hong explain me.

I mean that the OSPI0_ECC_FAIL pin should be connected to INT# of S28HS512T, but not used in AM64x-EVM. You can check on EVM Kit.

SoC, ECC_FAIL for external flash device where ECC is checked on the flash.

On the Flash device:

I also checked the OSPI node in DTS file, the ECC_FAIL pin did not configure.

Please scan your source code again, and can you help me how can I check an error (ECC) from OSPI device?

Maybe no need this ECC_FAIL pin to manage the ECC from flash device? Maybe I am wrong.

Many thank you for your supports

Thinh

Hey Thinh,

Thank you for the additional information and your patience. Just wanted to let you know I am still looking into this issue, and hope to have an answer within the next 1-2 business days.

Best regards,

Andrew

Hey Thinh,

Thank you for your patience and I apologize for the delay, just wanted to update you that we have reached out to a team with more specialized knowledge in this area, and we are currently awaiting their response. I will update you as soon as we hear back.

Best regards,

Andrew

Hello Thinh

Andrew forwarded this to me and Rahul. I believe we are already discussing this with you and your team offline. The ecc error interrupt handling is not currently enabled in the TI driver in our SDK . We have captured this as a future requirement.

Implementation timelines/SDK availability will need to be discussed in our offline discussions.

I will mark this thread closed.

Regards

Mukul