Other Parts Discussed in Thread: TLV320AIC3104, SN74AVC4T245

Hi Support Team,

I have the following question regarding the signals (McASP) between AM437x processor and CODEC (TLV320AIC3104).

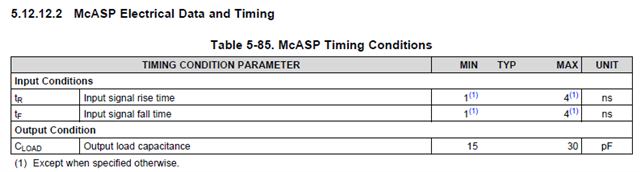

AM437x datasheet states that tR and tF for the following input signals are between 1 and 4ns.

I understand that this transition time is specified as 10 to 90% from the following forum response.

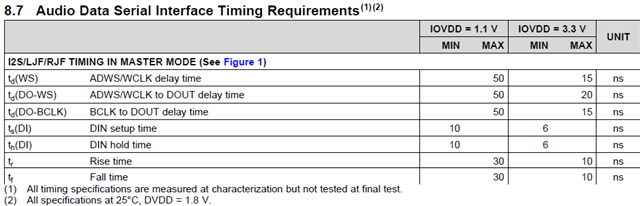

Also, CODEC datasheet states that tR and tF are ~10ns at IOVDD=3.3V.

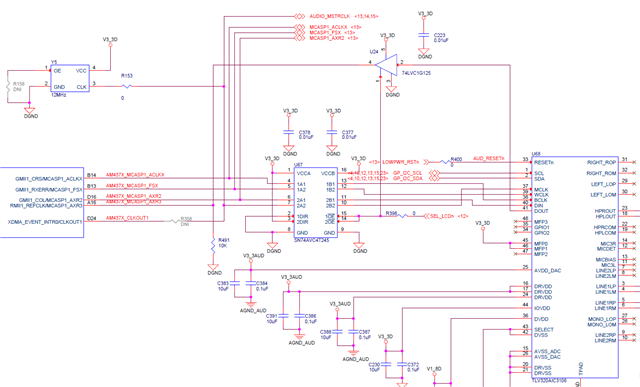

Currently, in my customer's prototype board, AM437x processor and CODEC (TLV320AIC3104) are connected via McASP (I2S).

The signal lines (WCLK, BCLK, Din, Dout) are directly connected between CPU and CODEC using CODEC as Master mode,

but the actual measurement of tR and tF of each signal WCLK, BCLK, Din, Dout is about 15ns,

which exceeds the maximum value of input signal transition time of CPU and CODEC.

So, here are questions.

Q1: For WCLK, BCLK, and Data timing requests (setup, hold), the current signal transition time of 15ns has enough margin,

but is this transition time acceptable?

If not, what kind of problem would be caused?

Q2: To achieve the transition time requirement, it is necessary to add a buffer between CPU and CODEC.

Referring to the AM437x evaluation board schematic, the connection is made via SN74AVC4T245 and 74LVC1G125 as shown below.

The datasheets for the SN74AVC4T245 and 74LVC1G125 could not be found any mention of transition times for the output signals.

How can I confirm that the transition time of the CPU's McASP input signal is 1 to 4 ns

and the transition time of the CODEC's I2S input signal is ~10 ns?

Best regards,

Kanae