Hi Expert,

layout user guide, Single-ended impedance TYP is 40 ohm +-10%. Differential impedance is 80 +-10%ohm

Is the evm also designed like this?

Thanks

Daniel

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Expert,

layout user guide, Single-ended impedance TYP is 40 ohm +-10%. Differential impedance is 80 +-10%ohm

Is the evm also designed like this?

Thanks

Daniel

Hello Daniel,

Thank you for the query.

The EVM follows the guidelines mentioned in the design guide.

FYI, both the EVMs GP and SK follow the guidelines.

Regards,

Sreenivasa

Hi Expert

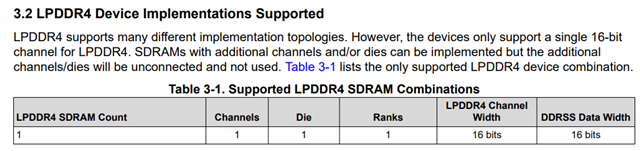

(1) AM6412 memory controller has CS0/CS1 two Chip select, we want to know whether the design of LPDDR4 x16 memory down supports dual rank application?

(2) DDR Board Design and Layout Guidelines write that CK, ADDR_CTRL, DQ, DM and other signals should not have stubs. Is there a back drill for the layer transition via of these signals on the public board?

If no back drill is done, how much length of via stub is allowed?

(3) How to set enabled in the LPDDR4 on-die termination software?

Thanks

Daniel

(1) AM6412 memory controller has CS0/CS1 two Chip select, we want to know whether the design of LPDDR4 x16 memory down supports dual rank application?

(3) How to set enabled in the LPDDR4 on-die termination software?

(20) AM6412: DDR4 ODT termination - Processors forum - Processors - TI E2E support forums

DDR Board Design and Layout Guidelines write that CK, ADDR_CTRL, DQ, DM and other signals should not have stubs. Is there a back drill for the layer transition via of these signals on the public board?

We recommend having queries related to specific topic in each thread to scale to other E2E users.

Please start a new thread with the title including DDR board design and layout. I may have to reassign the thread to experts.

Regards,

Sreenivasa