Part Number: AM6442

Other Parts Discussed in Thread: CDCI6214

Hello

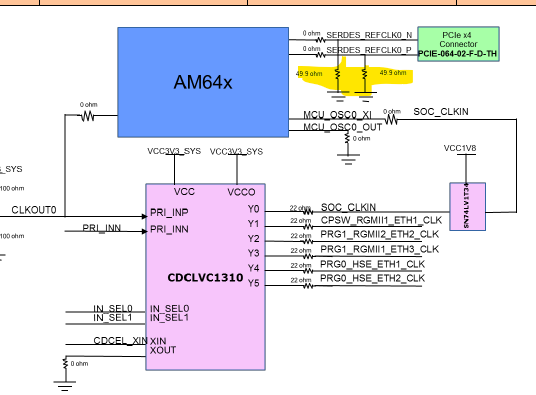

Let’s me add a related topic concerning electrical buffer of PCIe REFCLK.

SPRUJ63 (EVM GP user guide) mentioned 2 termination resistors of 49.9ohm, which could implies HCSL driver technology to be placed close to AM64 (as it is done in PCB):

But, all 5 schematics variants of EVM GP doesn’t include this (R622/R623) termination resistors, all DNI .

What should we do on that point ? Especially when we would like to manage both configuration : ROOT COMPLEX and ENDPOINT.

Thanks for your help