Hi Team,

Can I have information on the MAILBOX service? is MAILBOX accessible to the A53 and M4 cores or just the A53 cores? Is this mechanism an alternative for communicating to the M4 core?

BR,

-RT

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Ryan,

Thank you for the query.

To start with please refer to the below sections in the TRM.

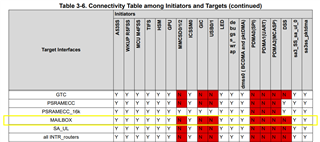

Table 3-6. Connectivity Table among Initiators and Targets (continued)

4.3.1 Mailbox

8.1 Mailbox

8.3 Interprocessor Communication Registers

10.1.3 Inter-processor Communication Scheme (IPC)

We have a FAQ with links to all the key collateral including the TRM. Please refer below.

Please provide the use case you are considering for us to be able to assign to the right expert or check internally for any additional queries you may have.

Regards,

Sreenivasa

Hi Sreenivasa,

The statements in the document are not very specific--I read this to imply that the A53 cores can use the mailbox to communicate, but the rest is rather uncertain. For example, the term "various on-chip processors" is very fuzzy--it does not directly translate to 'all' and if 'some', it does not say which ones.

Can I have some clarity here?

BR,

-RT

Hi Ryan,

As you can see, physical connectivity is present between all the processors (A53SS, WKUP R5FSS and MCU M4FSS) and the mailbox.

On the software end, mailbox is configured for communication between any two CPUs on the SOC, please refer to the IPC notify config driver (mcu_plus_sdk_am62x_08_05_00_09\source\drivers\ipc_notify\v0\soc\am62x\ipc_notify_v0_cfg.c) for more details about the pre-defined mailbox configurations.

/* Pre-defined mailbox config to allow any CPU to send and receive messages from any CPU on this SOC * * Each element consists of [maibox base addr, hw fifo, user id] * These assignments need to be in sync with gIpcNotifyInterruptConfig* done later below, * * This is a 2D array * - 1st indexed by source core ID * - then indexed by destination core ID * * FIFO Allocations * 0 : M4F -> A53 * 1 : A53 -> M4F * 2 : R5F -> A53 * 3 : A53 -> R5F * 4 : M4F -> R5F * 5 : R5F -> M4F * * User ID: * M4F Rx: 2 * R5F Rx: 1 * A53 Rx: 0 */

Do let me know if you have any more questions.

Regards,

Nitika