Other Parts Discussed in Thread: DRA821, DRA829, SYSCONFIG

How to change/generate the “Eth” configuration for MCAL Ethernet Application from one core to other core.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

How to change/generate the “Eth” configuration for MCAL Ethernet Application from one core to other core.

Default MCAL Ethernet Application supported for CPSW2G on MCU1_0, and Virtual Ethernet supported for CPSWnG (5G in case of DRA821 and 9G in case of DRA829 and J7AHP) on MCU2_1.

Please refer to the following link for the details about porting the MCAL application to other cores.

https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-jacinto7/08_06_01_03/exports/docs/mcusw/mcal_drv/docs/drv_docs/mcusw_c_ug_top.html#mcusw_c_ug_support_mcal_other_cores

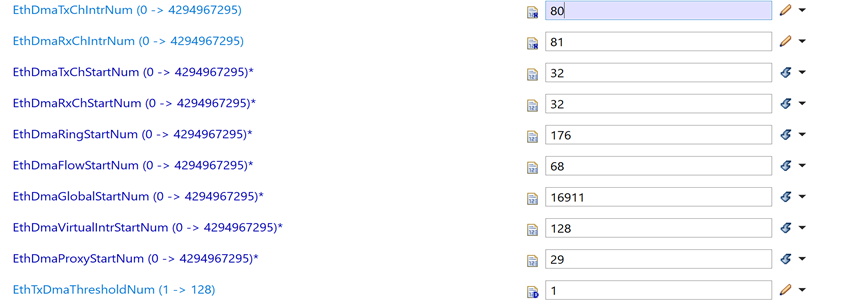

The Ethernet module depends on the UDMA for transmission/reception of ethernet data using Tx channels, Rx channels, Rx flows, and interrupts. We need to update these parameters for the desired/intended core where we want to run the application.

This FAQ talks about the generation of configuration using the EBtresos tool for other cores. Unfortunately, EBtresos may not be able to generate exact configuration files that directly work for other cores, so we need to make a few manual modifications after generating the configuration files from the EBtresos tool.

Configuration update from EBtresos tool:

Note: Above configuration is for the Ethernet application of CPSW2G in DRA821 for the MCU1_1 Core.

The above details can found in the .syscfg file specific to SOC (can be downloaded from Linux SDK and tool, also need to download sysconfig tool from https://www.ti.com/tool/SYSCONFIG)

Ex: j7200-evm.syscfg for DRA821.

Update the above parameters corresponding to the Core by referring to the .syscfg file and generate the configuration.

Apart from the above EBtresos tool configuration paraments update following manual changes are required.

1. Device ID configuration

In the config.h file below need to update with the Device ID specific to Core.

#define UDMA_DEVICE_ID_CORE 251

Note: Above Device ID is specific to MCU1_1 (MCU_R5FSS0_CORE1 ) core in DRA821.

Please refer to the TISCI document for the Device ID details of the Core.

https://software-dl.ti.com/tisci/esd/latest/5_soc_doc/j7200/devices.html

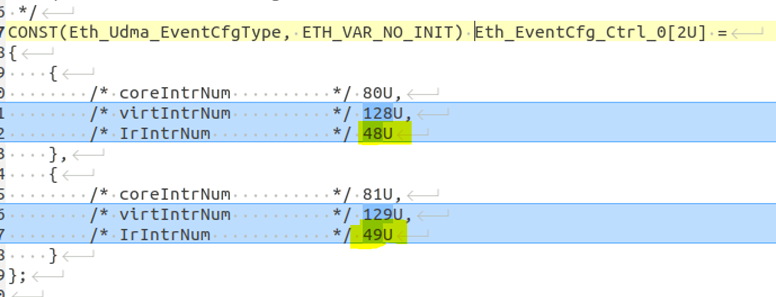

2. Out Interrupt number mapping to the Core

This mapping corresponds to the interrupt number configured above for UDMA Tx and Rx channels in the EBtresos tool.

In the config.c file under "Eth_EventCfg_Ctrl_0".

Note: Above interrupt numbers are for MCU1_1 Core.

Please refer to the “Interrupt Sources” section in TRM (technical reference manual) corresponding to SOC and check for intended core-specific interrupt mapping.

Also, refer to FAQ [How to Port MCAL Ethernet Virtual Mac application from MCU2_1 to MCU1_0] for reference.

Note:

Please update corresponding configuration files based on your build process as pre-build or linker or post-build as per above.