Other Parts Discussed in Thread: AM2434, CDCM61002, CDCM61001, LMK3H0102

Hi TI,

I'm working on a design which requires industrial ethernet (Profinet, EtherCAT, etc.) and real-time processing capabilities, in addition to higher level OS and graphics support. Per this thread, I'm leaning towards using an AM2434 for the industrial ethernet, real-time pre-processing, sensor interfacing, etc. requirements, coupled with a TDA4VE SoC for high performance/throughput processing, cryptography, and graphical output etc. using both RTOS and Embedded Linux environments. Per the above linked thread, connection between the AM2434 MCU and the TDA4VE SoC will be via PCIe (Gen2 x1).

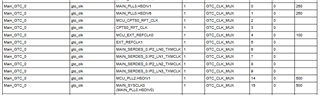

I need for each processor to maintain a precise internal timestamp, and I need for these timestamps/counters to be synchronized between each processor, such that a timestamped event on the MCU can be processed by the SoC using a common/synchronized time reference. To enable this functionality I'm considering the use of a dual-output clock generator (with low inter-channel skew) to drive 64-bit counters within each processor. The below block diagram provides a simplistic overview of the above:

Per the above, I have assumed the following:

- The CDCM61002 1:2 ultra-low jitter clock generator is a suitable part for this purpose.

- The GTC on both processors is a suitable 64-bit up-counter for this purpose.

- The EXT_REFCLK1 GTC source on both processors is suitable for this purpose.

Firstly, would you mind please confirming my three assumptions above?

Secondly, from the TDA4VE TRM (SPRUJ28C Table 5-25 Section 5.4.4.2), EXT_REFCLK1 is limited to 100MHz (of type LVCMOS); can you please confirm that this pertains to use of EXT_REFCLK1 as the source for GTC0, and that this 100MHz LVCMOS limit is common to the AM2434 MCU as well? I.e. if EXT_REFCLK1 feeding GTC0 is a suitable approach for this timestamp synchronisation function, is 100MHz the highest frequency counter input I'm able to achieve?

Lastly, for short clock trace lengths to these two processors (less than 100mm), do you think I will need LVCMOS buffers between each clock out of the CDCM61002 and its respective processor?

Conversely, instead of the dual output CDCM61002 clock generator, should I instead use a single output clock generator (e.g. CDCM61001) and a 1:2 LVCMOS buffer?

Thanks!