Hello TI experts,

It's about the DDR1 pins of TDA4AL-Q1.

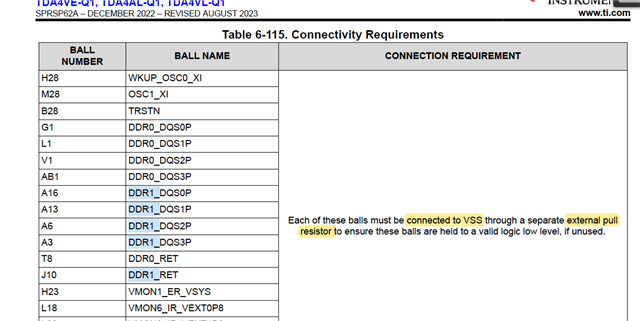

Since the TDA4L-Q1 doesn't have DDR1 module, so what to do with these pins such as DDR1_DQS0P? Must pull or just left open?

Especially for J14 VDDA_0P8_PLL_DDR1 and J12 VDDS_DDR_C1.

Thanks a lot.