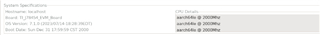

Part Number: J784S4XEVM

Environment:

Board: J784s4

PDK 9.01.00.06

qnx710

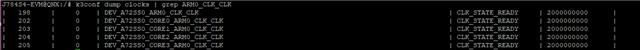

In QNX Momentics, the frequency appears as 2GHz:

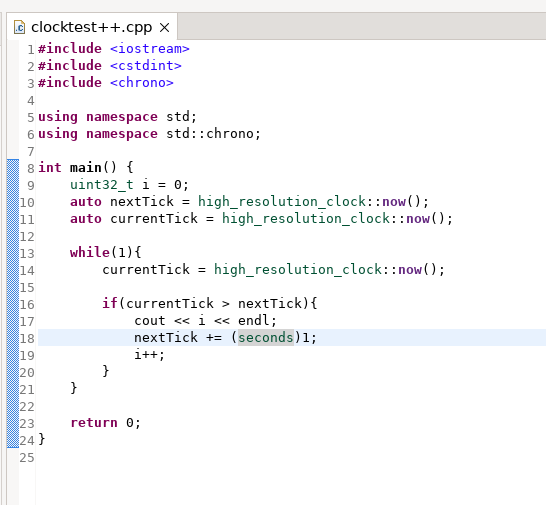

Running a simple program to check board timing, the j784s4 is reporting 25% ahead of actual time:

It seems that the clock frequency is configured to be variable or has a lower frequency than the reported 2GHz in QNX Momentics.

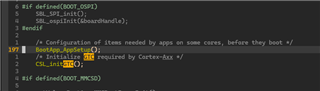

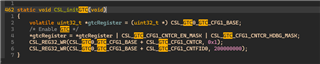

Could you please refer me to where we can configure the clock?

Thank you.