hi

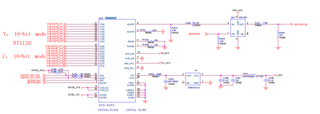

We want to output the bt1120 signal from the chip to the display adapter board. First, how can we output the bt1120 signal of 1280*720p(Because BT1120 to AHD requires the same format for input and output, and we only have 720 screens on our end)

hi

We want to output the bt1120 signal from the chip to the display adapter board. First, how can we output the bt1120 signal of 1280*720p(Because BT1120 to AHD requires the same format for input and output, and we only have 720 screens on our end)

Hello WU DAIWEI,

Thank you for the query.

I need you to explain your issues.

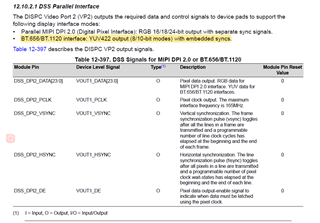

Refer below for mapping the DPI outputs.

Regards,

Sreenivasa

Hello WU DAIWEI,

Thank you.

Let me check and assign to the expert internally.

Regards,

Sreenivasa

Have you received a reply? Additionally, in our situation, how to port this feature can be referred to

Ti processor sdk linux-am62axx evm-08.06.00.45 \ board support \ Linux kernel \ drivers \ gpu \ drm \ bridge \ sii902x. c, porting tp2803

Hello WU DAIWEI,

Thank you.

I am assigning the thread to the expert to support.

Regards,

Sreenivasa

Please help send it to your experts

soft patch:

git diff board-support/linux-kernel/drivers/gpu/drm/bridge/sii902x.c board-support/linux-kernel/drivers/gpu/drm/tidss/tidss_dispc.c

diff --git a/ti-processor-sdk-linux-am62axx-evm-08.06.00.45/board-support/linux-kernel/drivers/gpu/drm/bridge/sii902x.c b/ti-processor-sdk-linux-am62axx-evm-08.06.00.45/board-support/linux-kernel/drivers/gpu/drm/bridge/sii902x.c

index 9e6b87c1e..0810322c5 100644

--- a/ti-processor-sdk-linux-am62axx-evm-08.06.00.45/board-support/linux-kernel/drivers/gpu/drm/bridge/sii902x.c

+++ b/ti-processor-sdk-linux-am62axx-evm-08.06.00.45/board-support/linux-kernel/drivers/gpu/drm/bridge/sii902x.c

@@ -261,13 +261,14 @@ static enum drm_connector_status sii902x_detect(struct sii902x *sii902x)

unsigned int status;

mutex_lock(&sii902x->mutex);

-

+#if 0

regmap_read(sii902x->regmap, SII902X_INT_STATUS, &status);

-

+#endif

mutex_unlock(&sii902x->mutex);

- return (status & SII902X_PLUGGED_STATUS) ?

- connector_status_connected : connector_status_disconnected;

+ //return (status & SII902X_PLUGGED_STATUS) ?

+ // connector_status_connected : connector_status_disconnected;

+ return connector_status_connected;

}

static enum drm_connector_status

@@ -312,13 +313,17 @@ static int sii902x_get_modes(struct drm_connector *connector)

struct sii902x *sii902x = connector_to_sii902x(connector);

struct edid *edid;

int num = 0;

-

+#if 0

edid = sii902x_get_edid(sii902x, connector);

drm_connector_update_edid_property(connector, edid);

if (edid) {

num = drm_add_edid_modes(connector, edid);

kfree(edid);

}

+#endif

+ num = drm_add_modes_noedid(connector, 1280, 720);

+ drm_set_preferred_mode(connector, 1280, 720);

+

return num;

}

@@ -341,11 +346,11 @@ static void sii902x_bridge_disable(struct drm_bridge *bridge)

struct sii902x *sii902x = bridge_to_sii902x(bridge);

printk("zyk %s %d\n",__func__,__LINE__);

mutex_lock(&sii902x->mutex);

-

+#if 0

regmap_update_bits(sii902x->regmap, SII902X_SYS_CTRL_DATA,

SII902X_SYS_CTRL_PWR_DWN,

SII902X_SYS_CTRL_PWR_DWN);

-

+#endif

mutex_unlock(&sii902x->mutex);

}

@@ -354,12 +359,14 @@ static void sii902x_bridge_enable(struct drm_bridge *bridge)

struct sii902x *sii902x = bridge_to_sii902x(bridge);

printk("zyk %s %d\n",__func__,__LINE__);

mutex_lock(&sii902x->mutex);

+#if 0

regmap_update_bits(sii902x->regmap, SII902X_PWR_STATE_CTRL,

SII902X_AVI_POWER_STATE_MSK,

SII902X_AVI_POWER_STATE_D(0));

regmap_update_bits(sii902x->regmap, SII902X_SYS_CTRL_DATA,

SII902X_SYS_CTRL_PWR_DWN, 0);

+#endif

mutex_unlock(&sii902x->mutex);

}

@@ -393,6 +400,7 @@ printk("zyk %s %d\n",__func__,__LINE__);

SII902X_TPI_AVI_INPUT_COLORSPACE_RGB;

mutex_lock(&sii902x->mutex);

+#if 0

ret = regmap_update_bits(sii902x->regmap, SII902X_SYS_CTRL_DATA,

SII902X_SYS_CTRL_OUTPUT_MODE, output_mode);

@@ -402,7 +410,7 @@ printk("zyk %s %d\n",__func__,__LINE__);

ret = regmap_bulk_write(regmap, SII902X_TPI_VIDEO_DATA, buf, 10);

if (ret)

goto out;

-

+#endif

ret = drm_hdmi_avi_infoframe_from_display_mode(&frame,

&sii902x->connector, adj);

if (ret < 0) {

@@ -415,12 +423,13 @@ printk("zyk %s %d\n",__func__,__LINE__);

DRM_ERROR("failed to pack AVI infoframe: %d\n", ret);

goto out;

}

+#if 0

/* Do not send the infoframe header, but keep the CRC field. */

regmap_bulk_write(regmap, SII902X_TPI_AVI_INFOFRAME,

buf + HDMI_INFOFRAME_HEADER_SIZE - 1,

HDMI_AVI_INFOFRAME_SIZE + 1);

-

+#endif

out:

mutex_unlock(&sii902x->mutex);

}

@@ -429,7 +438,7 @@ static int sii902x_bridge_attach(struct drm_bridge *bridge,

enum drm_bridge_attach_flags flags)

{

struct sii902x *sii902x = bridge_to_sii902x(bridge);

- u32 bus_format =MEDIA_BUS_FMT_UYVY8_2X8; //MEDIA_BUS_FMT_RGB888_1X24;//MEDIA_BUS_FMT_YUYV8_1X16;

+ u32 bus_format =MEDIA_BUS_FMT_UYVY8_1X16;//MEDIA_BUS_FMT_UYVY8_1X16;//MEDIA_BUS_FMT_RGB565_1X16;//MEDIA_BUS_FMT_UYVY8_2X8;//MEDIA_BUS_FMT_RGB565_1X16;//MEDIA_BUS_FMT_UYVY8_2X8; //MEDIA_BUS_FMT_RGB888_1X24;//MEDIA_BUS_FMT_YUYV8_1X16;

struct drm_device *drm = bridge->dev;

int ret;

printk("zyk %s %d\n",__func__,__LINE__);

@@ -1153,6 +1162,80 @@ static const struct sii902x_reg init_regs[] = {

{0xF5,0x00},

};

+static const struct sii902x_reg tvi_init_regs[] = {

+ {0xFF,0x00},

+ {0x00,0x00},

+ {0x01,0x00},

+ {0x02,0xCB},

+ {0x03,0x42},

+ {0x04,0x00},

+ {0x05,0x46},

+ {0x06,0x00},

+ {0x07,0x41},

+ {0x08,0x6E},

+ {0x09,0x28},

+ {0x0A,0x28},

+ {0x0B,0x05},

+ {0x0C,0x04},

+ {0x0D,0x04},

+ {0x0E,0x28},

+ {0x0F,0x72},

+ {0x10,0x06},

+ {0x11,0x83},

+ {0x12,0x05},

+ {0x13,0x3C},

+ {0x14,0x38},

+ {0x15,0x38},

+ {0x16,0xEB},

+ {0x17,0x08},

+ {0x18,0x00},

+ {0x19,0xF0},

+ {0x1A,0x10},

+ {0x1B,0xA4},

+ {0x1C,0x55},

+ {0x1D,0x76},

+ {0x1E,0x80},

+ {0x1F,0x00},

+ {0x20,0x48},

+ {0x21,0xBA},

+ {0x22,0x2E},

+ {0x23,0x8B},

+ {0x24,0x86},

+ {0x25,0x40},

+ {0x26,0x00},

+ {0x27,0x56},

+ {0x28,0x00},

+ {0x29,0x35},

+ {0x2A,0x19},

+ {0x2B,0x78},

+ {0x2C,0x60},

+ {0x2D,0x00},

+ {0x2E,0x00},

+ {0x2F,0x00},

+ {0x30,0x01},

+ {0x31,0x00},

+ {0x32,0x00},

+ {0x33,0x00},

+ {0x34,0x00},

+ {0x35,0x00},

+ {0x36,0x00},

+ {0x37,0x00},

+ {0x38,0x00},

+ {0x39,0x00},

+ {0x3A,0x00},

+ {0x3B,0xD0},

+ {0x3C,0x10},

+ {0x3D,0x80},

+ {0x3E,0x18},

+ {0x3F,0x00},

+ {0x45,0x40},

+ {0xF0,0x00},

+ {0xF1,0x08},

+ {0xF2,0x2a},

+ {0xF3,0x4a},

+ {0xF4,0x61},

+ {0xF5,0x00},

+};

static int sii9022_write_reg(struct sii902x *sii902x, u8 reg, u8 val)

{

struct i2c_client *client = sii902x->i2c;

diff --git a/ti-processor-sdk-linux-am62axx-evm-08.06.00.45/board-support/linux-kernel/drivers/gpu/drm/tidss/tidss_dispc.c b/ti-processor-sdk-linux-am62axx-evm-08.06.00.45/board-support/linux-kernel/drivers/gpu/drm/tidss/tidss_dispc.c

index 5571ddfe3..d06a38445 100644

--- a/ti-processor-sdk-linux-am62axx-evm-08.06.00.45/board-support/linux-kernel/drivers/gpu/drm/tidss/tidss_dispc.c

+++ b/ti-processor-sdk-linux-am62axx-evm-08.06.00.45/board-support/linux-kernel/drivers/gpu/drm/tidss/tidss_dispc.c

@@ -3,7 +3,7 @@

* Copyright (C) 2016-2018 Texas Instruments Incorporated - https://www.ti.com/

* Author: Jyri Sarha <jsarha@ti.com>

*/

-

+#define DEBUG

#include <linux/clk.h>

#include <linux/delay.h>

#include <linux/dma-mapping.h>

@@ -864,7 +864,11 @@ struct dispc_bus_format {

static const struct dispc_bus_format dispc_bus_formats[] = {

{ MEDIA_BUS_FMT_RGB444_1X12, 12, false, 0 },

{ MEDIA_BUS_FMT_RGB565_1X16, 16, false, 0 },

- { MEDIA_BUS_FMT_RGB666_1X18, 18, false, 0 },

+ { MEDIA_BUS_FMT_RGB666_1X18, 18, false, 0 },

+ { MEDIA_BUS_FMT_UYVY8_2X8, 16, false, 0 },

+ { MEDIA_BUS_FMT_UYVY8_1X16, 20, false, 0 },

+

+ { MEDIA_BUS_FMT_YUYV8_1X16, 16, false, 0 },

{ MEDIA_BUS_FMT_RGB888_1X24, 24, false, 0 },

{ MEDIA_BUS_FMT_RGB101010_1X30, 30, false, 0 },

{ MEDIA_BUS_FMT_RGB121212_1X36, 36, false, 0 },

@@ -2916,16 +2920,18 @@ int dispc_init(struct tidss_device *tidss)

u32 gamma_size = dispc->feat->vp_feat.color.gamma_size;

u32 *gamma_table;

struct clk *clk;

-

+ dev_warn(dev, "%s %d name:%s\n",__func__,__LINE__,dispc->feat->ovr_name[i]);

r = dispc_iomap_resource(pdev, dispc->feat->ovr_name[i],

&dispc->base_ovr[i]);

if (r)

return r;

+ dev_warn(dev, "%s %d name:%s\n",__func__,__LINE__,dispc->feat->vp_name[i]);

r = dispc_iomap_resource(pdev, dispc->feat->vp_name[i],

&dispc->base_vp[i]);

if (r)

return r;

+ dev_warn(dev, "%s %d name:%s\n",__func__,__LINE__,dispc->feat->vpclk_name[i]);

clk = devm_clk_get(dev, dispc->feat->vpclk_name[i]);

if (IS_ERR(clk)) {

@@ -2970,6 +2976,7 @@ int dispc_init(struct tidss_device *tidss)

&dispc->memory_bandwidth_limit);

tidss->dispc = dispc;

+ dev_warn(dev, "%s %d \n",__func__,__LINE__);

return 0;

}

(END)

modetest -M tidss

root@am62axx-evm:~#

root@am62axx-evm:~# modetest -M tidss

Encoders:

id crtc type possible crtcs possible clones

38 37 none 0x00000001 0x00000001

Connectors:

id encoder status name size (mm) modes encoders

39 38 connected HDMI-A-1 0x0 5 38

modes:

index name refresh (Hz) hdisp hss hse htot vdisp vss vse vtot)

#0 1280x720 60.00 1280 1390 1430 1650 720 725 730 750 74250 flags: phsync, pvsync; type: preferred, driver

#1 800x600 60.32 800 840 968 1056 600 601 605 628 40000 flags: phsync, pvsync; type: driver

#2 800x600 56.25 800 824 896 1024 600 601 603 625 36000 flags: phsync, pvsync; type: driver

#3 848x480 60.00 848 864 976 1088 480 486 494 517 33750 flags: phsync, pvsync; type: driver

#4 640x480 59.94 640 656 752 800 480 490 492 525 25175 flags: nhsync, nvsync; type: driver

props:

1 EDID:

flags: immutable blob

blobs:

value:

2 DPMS:

flags: enum

enums: On=0 Standby=1 Suspend=2 Off=3

value: 0

5 link-status:

flags: enum

enums: Good=0 Bad=1

value: 0

6 non-desktop:

flags: immutable range

values: 0 1

value: 0

4 TILE:

flags: immutable blob

blobs:

value:

20 CRTC_ID:

flags: object

value: 37

CRTCs:

id fb pos size

37 46 (0,0) (1280x720)

#0 1280x720 60.00 1280 1390 1430 1650 720 725 730 750 74250 flags: phsync, pvsync; type: preferred, driver

props:

22 ACTIVE:

flags: range

values: 0 1

value: 1

23 MODE_ID:

flags: blob

blobs:

value:

0a22010000056e05960572060000d002

d502da02ee0200003c00000005000000

48000000313238307837323000000000

00000000000000000000000000000000

00000000

19 OUT_FENCE_PTR:

flags: range

values: 0 18446744073709551615

value: 0

24 VRR_ENABLED:

flags: range

values: 0 1

value: 0

27 CTM:

flags: blob

blobs:

value:

28 GAMMA_LUT:

flags: blob

blobs:

value:

29 GAMMA_LUT_SIZE:

flags: immutable range

values: 0 4294967295

value: 256

Planes:

id crtc fb CRTC x,y x,y gamma size possible crtcs

31 37 46 0,0 0,0 0 0x00000001

formats: AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 XR15 XB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12

props:

8 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 1

17 FB_ID:

flags: object

value: 46

18 IN_FENCE_FD:

flags: signed range

values: -1 2147483647

value: -1

20 CRTC_ID:

flags: object

value: 37

13 CRTC_X:

flags: signed range

values: -2147483648 2147483647

value: 0

14 CRTC_Y:

flags: signed range

values: -2147483648 2147483647

value: 0

15 CRTC_W:

flags: range

values: 0 2147483647

value: 1280

16 CRTC_H:

flags: range

values: 0 2147483647

value: 720

9 SRC_X:

flags: range

values: 0 4294967295

value: 0

10 SRC_Y:

flags: range

values: 0 4294967295

value: 0

11 SRC_W:

flags: range

values: 0 4294967295

value: 83886080

12 SRC_H:

flags: range

values: 0 4294967295

value: 47185920

32 zpos:

flags: range

values: 0 1

value: 0

33 COLOR_ENCODING:

flags: enum

enums: ITU-R BT.601 YCbCr=0 ITU-R BT.709 YCbCr=1

value: 0

34 COLOR_RANGE:

flags: enum

enums: YCbCr limited range=0 YCbCr full range=1

value: 0

35 alpha:

flags: range

values: 0 65535

value: 65535

36 pixel blend mode:

flags: enum

enums: Pre-multiplied=0 Coverage=1

value: 0

40 0 0 0,0 0,0 0 0x00000001

formats: AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 XR15 XB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12

props:

8 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 0

17 FB_ID:

flags: object

value: 0

18 IN_FENCE_FD:

flags: signed range

values: -1 2147483647

value: -1

20 CRTC_ID:

flags: object

value: 0

13 CRTC_X:

flags: signed range

values: -2147483648 2147483647

value: 0

14 CRTC_Y:

flags: signed range

values: -2147483648 2147483647

value: 0

15 CRTC_W:

flags: range

values: 0 2147483647

value: 0

16 CRTC_H:

flags: range

values: 0 2147483647

value: 0

9 SRC_X:

flags: range

values: 0 4294967295

value: 0

10 SRC_Y:

flags: range

values: 0 4294967295

value: 0

11 SRC_W:

flags: range

values: 0 4294967295

value: 0

12 SRC_H:

flags: range

values: 0 4294967295

value: 0

41 zpos:

flags: range

values: 0 1

value: 0

42 COLOR_ENCODING:

flags: enum

enums: ITU-R BT.601 YCbCr=0 ITU-R BT.709 YCbCr=1

value: 0

43 COLOR_RANGE:

flags: enum

enums: YCbCr limited range=0 YCbCr full range=1

value: 0

44 alpha:

flags: range

values: 0 65535

value: 65535

45 pixel blend mode:

flags: enum

enums: Pre-multiplied=0 Coverage=1

value: 0

Frame buffers:

id size pitch

root@am62axx-evm:~#

two questions:

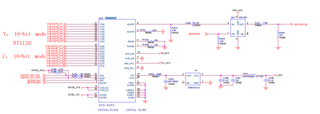

1.about pclk:

My goal is to output data in bt1120 format (16bit)with a resolution of 1280x720 to tp2803, but now I have measured that the clock is 74.25M, which should be 37.125M

2.about data:

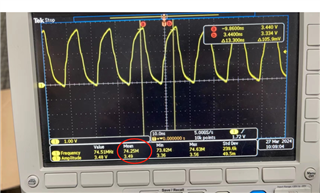

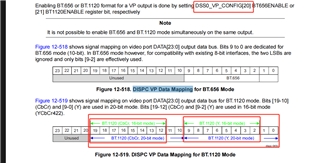

Where is this DISPC VP Data Mapping (not pinmux) configured,

DSS0_VP-CONFIG [20] BT656ENABLE or

[21] BT1120ENABLE register bit,

Devmem2 0x3020b000 w 0x01600004

Devmem2 0x3020A000 w 0x01600004

In VOUT0-DATA0-VOUT0-DATA19, there is a signal in the data line 0,1,10,11, which is different from the target

Is there any problem with my modifications? Why are the clocks and measured signals incorrect

Please answer my two questions about clock and data one by one!!!

thank you.

Hi,

I am checking internally and I will get back to you by end of the day.

Regards,

Krunal

Hi,

I checked internally and wanted to share the following background:

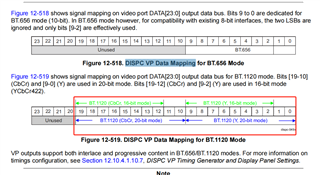

1. If you are using our EVM for BT656 testing, you would need to modify the HW connections between DSS and SII9022A. For example, refer to data mapping in: Figure 12-518. DISPC VP Data Mapping for BT.656 Mode

2. The SII9022A only supports input format of RGB so you would need to customize the driver to add support for YUV. The driver is not maintained by TI so you would need to check for support with community.

3. Since our EVM does not support BT656, we need to add support for it in the TIDSS driver. At the moment, support is not included since we do not have local support for it in our EVM.

Your questions:

1. What are you programming in the SIL driver for the 1280x720 resolution. I am curious why you are expecting 32MHz because bridge chips usually request a frequency from TIDSS. Are you requesting for 32MHz and seeing 72MHz?

2. in terms of your experiment, there is a bug in the TRM and the address of the VP1 register is incorrect. It should be 0x3020B000 instead of 0x3020A000. Also, the config register is shadow register so you need to set GO BIT in control register (0x3020B004 bit 5) as well.

Regards,

Krunal

Firstly, we will debug on our board. The wiring is 16bit and the format is BT1120, not BT656

1. What are you programming in the SIL driver for the 1280x720 resolution. I am curious why you are expecting 32MHz because bridge chips usually request a frequency from TIDSS. Are you requesting for 32MHz and seeing 72MHz?

tp2803's format

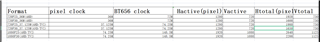

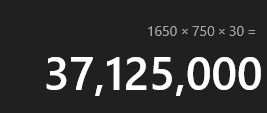

If I choose the bt1120 format, format 7720P30_17.125M (AND/TVI)

PCLK should not be

Htol * vtol * fps=3712500

2. in terms of your experiment, there is a bug in the TRM and the address of the VP1 register is incorrect. It should be 0x3020B000 instead of 0x3020A000. Also, the config register is shadow register so you need to set GO BIT in control register (0x3020B004 bit 5) as well.

to send below command, now it's like before

In VOUT0-DATA0-VOUT0-DATA19, there is a signal in the data line 0,1,10,11, which is different from the target

devmem2 0x3020b000 w 0x00200004

devmem2 0x3020b004 w 0x00000361

Hi,

#1. Your modetest shows 1280x720 60 FPS but for your calculation, you seem to use 30 FPS. Are you sure your programing the right resolution/fps?

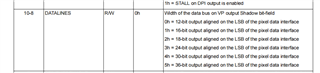

#2. For the 0x3020b004, you are programming 0x361 and if you refer to the field "DATALINES" (bit 10-8), you are programming 24bit.

Regards,

Krunal

#1. Your modetest shows 1280x720 60 FPS but for your calculation, you seem to use 30 FPS. Are you sure your programing the right resolution/fps?

I upload my new log,It is 30fps?

CRTCs:

id fb pos size

37 46 (0,0) (1280x720)

#0 1280x720 29.09 1280 1390 1430 1650 720 725 730 750 36000 flags: phsync, pvsync; type: preferred, driver

props:

root@am62axx-evm:~# modetest -M tidss

Encoders:

id crtc type possible crtcs possible clones

38 37 none 0x00000001 0x00000001

Connectors:

id encoder status name size (mm) modes encoders

39 38 connected HDMI-A-1 0x0 5 38

modes:

index name refresh (Hz) hdisp hss hse htot vdisp vss vse vtot)

#0 1280x720 29.09 1280 1390 1430 1650 720 725 730 750 36000 flags: phsync, pvsync; type: preferred, driver

#1 800x600 60.32 800 840 968 1056 600 601 605 628 40000 flags: phsync, pvsync; type: driver

#2 800x600 56.25 800 824 896 1024 600 601 603 625 36000 flags: phsync, pvsync; type: driver

#3 848x480 60.00 848 864 976 1088 480 486 494 517 33750 flags: phsync, pvsync; type: driver

#4 640x480 59.94 640 656 752 800 480 490 492 525 25175 flags: nhsync, nvsync; type: driver

props:

1 EDID:

flags: immutable blob

blobs:

value:

2 DPMS:

flags: enum

enums: On=0 Standby=1 Suspend=2 Off=3

value: 0

5 link-status:

flags: enum

enums: Good=0 Bad=1

value: 0

6 non-desktop:

flags: immutable range

values: 0 1

value: 0

4 TILE:

flags: immutable blob

blobs:

value:

20 CRTC_ID:

flags: object

value: 37

CRTCs:

id fb pos size

37 46 (0,0) (1280x720)

#0 1280x720 29.09 1280 1390 1430 1650 720 725 730 750 36000 flags: phsync, pvsync; type: preferred, driver

props:

22 ACTIVE:

flags: range

values: 0 1

value: 1

23 MODE_ID:

flags: blob

blobs:

value:

a08c000000056e05960572060000d002

d502da02ee0200001d00000005000000

48000000313238307837323000000000

00000000000000000000000000000000

00000000

19 OUT_FENCE_PTR:

flags: range

values: 0 18446744073709551615

value: 0

24 VRR_ENABLED:

flags: range

values: 0 1

value: 0

27 CTM:

flags: blob

blobs:

value:

28 GAMMA_LUT:

flags: blob

blobs:

value:

29 GAMMA_LUT_SIZE:

flags: immutable range

values: 0 4294967295

value: 256

Planes:

id crtc fb CRTC x,y x,y gamma size possible crtcs

31 37 46 0,0 0,0 0 0x00000001

formats: AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 XR15 XB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12

props:

8 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 1

17 FB_ID:

flags: object

value: 46

18 IN_FENCE_FD:

flags: signed range

values: -1 2147483647

value: -1

20 CRTC_ID:

flags: object

value: 37

13 CRTC_X:

flags: signed range

values: -2147483648 2147483647

value: 0

14 CRTC_Y:

flags: signed range

values: -2147483648 2147483647

value: 0

15 CRTC_W:

flags: range

values: 0 2147483647

value: 1280

16 CRTC_H:

flags: range

values: 0 2147483647

value: 720

9 SRC_X:

flags: range

values: 0 4294967295

value: 0

10 SRC_Y:

flags: range

values: 0 4294967295

value: 0

11 SRC_W:

flags: range

values: 0 4294967295

value: 83886080

12 SRC_H:

flags: range

values: 0 4294967295

value: 47185920

32 zpos:

flags: range

values: 0 1

value: 0

33 COLOR_ENCODING:

flags: enum

enums: ITU-R BT.601 YCbCr=0 ITU-R BT.709 YCbCr=1

value: 0

34 COLOR_RANGE:

flags: enum

enums: YCbCr limited range=0 YCbCr full range=1

value: 0

35 alpha:

flags: range

values: 0 65535

value: 65535

36 pixel blend mode:

flags: enum

enums: Pre-multiplied=0 Coverage=1

value: 0

40 0 0 0,0 0,0 0 0x00000001

formats: AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 XR15 XB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12

props:

8 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 0

17 FB_ID:

flags: object

value: 0

18 IN_FENCE_FD:

flags: signed range

values: -1 2147483647

value: -1

20 CRTC_ID:

flags: object

value: 0

13 CRTC_X:

flags: signed range

values: -2147483648 2147483647

value: 0

14 CRTC_Y:

flags: signed range

values: -2147483648 2147483647

value: 0

15 CRTC_W:

flags: range

values: 0 2147483647

value: 0

16 CRTC_H:

flags: range

values: 0 2147483647

value: 0

9 SRC_X:

flags: range

values: 0 4294967295

value: 0

10 SRC_Y:

flags: range

values: 0 4294967295

value: 0

11 SRC_W:

flags: range

values: 0 4294967295

value: 0

12 SRC_H:

flags: range

values: 0 4294967295

value: 0

41 zpos:

flags: range

values: 0 1

value: 0

42 COLOR_ENCODING:

flags: enum

enums: ITU-R BT.601 YCbCr=0 ITU-R BT.709 YCbCr=1

value: 0

43 COLOR_RANGE:

flags: enum

enums: YCbCr limited range=0 YCbCr full range=1

value: 0

44 alpha:

flags: range

values: 0 65535

value: 65535

45 pixel blend mode:

flags: enum

enums: Pre-multiplied=0 Coverage=1

value: 0

Frame buffers:

id size pitch

#2. For the 0x3020b004, you are programming 0x361 and if you refer to the field "DATALINES" (bit 10-8), you are programming 24bit.

I send below command,

devmem2 0x3020b000 w 0x00200004

devmem2 0x3020b004 w 0x00000341

now it's like before ,

In VOUT0-DATA0-VOUT0-DATA19, there is a signal in the data line 0,1,10,11, which is different from the target

send devmem2 0x3020b004 w 0x00000161,and got nothing

The total line used here is VOUT0-D2-VOUT0-D9 VOUT0-D12-VOUT0-D19. There are only a few values set, which one should I set

by the way,The color bar function of my module(Module tp2803 internally issued) can now light up on the screen, but the SOC data is not correct yet

the screen format is 1280*720 25hz

We have not tested BT656 on our platforms and we cannot use SII9022A(HDMI converter) as a reference because the driver does not support BT656. For all we know it could be requesting DSS to output in RGB mode since that's all it supports.

Regards,

Krunal

I know that the default output of SII9022A (HDMI converter) DSS is in RGB format. What I mean is to modify it to output data in the form of the BT1120 interface (these data are not interactive, but you can measure the waveform with an oscilloscope after modification. We only used 16 wires, so let's test if there is a waveform on those 16 wires first). How can we modify it?

Can you understand what I mean

Isn't bt1120 in YUV422 format? According to your chip manual, TRM says it supports it

Yes I understand and we do support bt1120. However, we have not tested that mode since our DSS and SII on the EVM are connected in such a manner that it outputs RGB mode only. Based on my internal discussions with SW dev team, few things to consider:

1. Input buffer: There is a CSC conversion for YUV to RGB in the videpipeline. If you are inputting YUV formats, you will need to program the coefficints for the CSC converter.

2. Overlay manager: It expects RGB and then there is a CSC conversion from RGB to YUV for Video Port(output). You also need to program the coefficient for the CSC converter.

3. Enable BT mode and verify the signal. I understand that other lines are toggling but is the data present on lines VOUT0-D2-VOUT0-D9 VOUT0-D12-VOUT0-D1 accurate?

Regards,

Krunal

Hi,

I was internally talking with my HW IP colleague and he mentioned it should be as simple as setting the BT bit in the VP config register. Also, what test are you running while data is toggling? Because the internal colorbar test will output and toggle all the RGB bits (no support for BT) and kmstest will also output in RGB24 format.

Regards,

Krunal

I have read your two replies and I will take two questions from them to explain (because I really don't know how to program CSC)

A:

-----------------------------------------------------------------------------------------------------------------------------------------------------

I was internally talking with my HW IP colleague and he mentioned it should be as simple as setting the BT bit in the VP config register. Also, what test are you running while data is toggling?

my steps:

Set bit 21 of DISCCVP_CONFIG in the code to ensure that bit 21 has been set after startup

--- a/ti-processor-sdk-linux-am62axx-evm-08.06.00.45/board-support/linux-kernel/drivers/gpu/drm/tidss/tidss_dispc.c

+++ b/ti-processor-sdk-linux-am62axx-evm-08.06.00.45/board-support/linux-kernel/drivers/gpu/drm/tidss/tidss_dispc.c

@@ -2571,6 +2575,7 @@ static void dispc_k2g_vp_set_ctm(struct dispc_device *dispc, u32 hw_videoport,

cprenable = 1;

}

+ VP_REG_FLD_MOD(dispc, hw_videoport, DISPC_VP_CONFIG, 1, 21, 21);

VP_REG_FLD_MOD(dispc, hw_videoport, DISPC_VP_CONFIG,

cprenable, 15, 15);

}

@@ -2637,6 +2642,7 @@ static void dispc_k3_vp_set_ctm(struct dispc_device *dispc, u32 hw_videoport,

colorconvenable = 1;

}

+ VP_REG_FLD_MOD(dispc, hw_videoport, DISPC_VP_CONFIG, 1, 21, 21);

VP_REG_FLD_MOD(dispc, hw_videoport, DISPC_VP_CONFIG,

colorconvenable, 24, 24);

}

[ OK ] Started syslog.service.

[ OK ] Started LSB: Expand Rootfs of boot device.

_____ _____ _ _

| _ |___ ___ ___ ___ | _ |___ ___ |_|___ ___| |_

| | _| .'| . | . | | __| _| . | | | -_| _| _|

|__|__|_| |__,|_ |___| |__| |_| |___|_| |___|___|_|

|___| |___|

Arago Project am62axx-evm ttyS2

Arago 2021.09 am62axx-evm ttyS2

am62axx-evm login: [ 29.385705] am65-cpsw-nuss 8000000.ethernet eth0: Link is Up - 100Mbps/Full - flow control off

[ 29.394350] IPv6: ADDRCONF(NETDEV_CHANGE): eth0: link becomes ready

[ 43.287213] Initializing XFRM netlink socket

am62axx-evm login: root

root@am62axx-evm:~# devmem2 0x3020b000

/dev/mem opened.

Memory mapped at address 0xffffa1bf1000.

Read at address 0x3020B000 (0xffffa1bf1000): 0x00200004

root@am62axx-evm:~#

modetest -M tidss -s 39@37:1280x720@UYVY -P 31@37:1280x720

setting mode 1280x720-29.09Hz@UYVY on connectors 39, crtc 37

testing 1280x720@XR24 overlay plane 31

then Afterwards, measure the signal

In VOUT0-DATA0~VOUT0-DATA19, there is a signal in the data line 0,1,10,11, which is different from the target

B:

-----------------------------------------------------------------------------------------------------------------------------------------------------

3. Enable BT mode and verify the signal. I understand that other lines are toggling but is the data present on lines VOUT0-D2-VOUT0-D9 VOUT0-D12-VOUT0-D1 accurate?

I don't know if these data are accurate either. According to the manufacturer TP2803, the SOC only needs to send the corresponding data to the BT1120 interface, and the converter can display it. I just need to turn off the color bar (my experiments have all turned off the color bar)

regarding the content of the VOUT0-D2~VOUT0-D9 and VOUT0-D12~VOUT0-D19 data cables, what is the data situation I measured using an oscilloscope

Data is available for VOUT0-DATA0~VOUT0-DATA19, but not for VOUT0-DATA20~VOUT0-DATA23

My problem is that according to the TRM manual, there should not be any data coming out for these lines VOUT0-DATA0, VOUT0-DATA1, VOUT0-DATA10, and VOUT0-DATA11, but I don't know where to control them. From the logs above, I have set bit 21 of DISCCVP_CONFIG. This data roadmap should only have waveforms for the VOUT0-D2~VOUT0-D9 and VOUT0-D12~VOUT0-D19 data lines

Understood but I believe the modetest will output in RGB mode and only input is YUV. That's why you are observing other data lines to toggle and I will confirm with our SW dev team.

Regards,

Krunal

Attempting to output yuv using gst launch, but the same phenomenon persists. May I ask when your sw dev team can come to a conclusion

gst-launch-1.0 v4l2src device=/dev/video2 ! video/x-raw,format=YUY2,width=1280,height=720,framerate=15/1 ! videorate ! videoscale ! videoconvert ! kmssink sync=false driver-name=tidss Setting pipeline to PAUSED ... Pipeline is live and does not need PREROLL ... Setting pipeline to PLAYING ... New clock: GstSystemClock [ 4580.417389] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4580.470409] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4580.542271] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4580.615505] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4580.681904] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4580.750698] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4580.819421] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4580.888094] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4580.956976] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4581.025732] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4581.094421] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4581.163206] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4581.232024] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4581.305098] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4581.378178] dispc_vid_csc_setup 1634 encoding 0 color_range0 [ 4581.434768] dispc_vid_csc_setup 1634 encoding 0 color_range0

Is there anyone else who could answer my question

I try to send below command,and got nothing

modetest -M tidss -s 39@37:1280x720@UYVY-16@25 -P 31@37:1280x720@UYVY-16@25 setting mode 1280x720-60.00Hz@UYVY on connectors 39, crtc 37 testing 1280x720@UYVY overlay plane 31

Hi,

modetest will output in RGB format because it will negotiate with SII/TIDSS driver for available output formats. Since we only support RGB, that's what will be observed on output.

Regards,

Krunal

I send below command,My monitor keeps flashing

systemctl stop weston.service

gst-launch-1.0 videotestsrc num-buffers=10000 is-live=true pattern=smpte ! "video/x-raw,format=RGB, width=1280, height=720" ! kmssink driver-name=tidss bus-id=37 display-height=1280 display-height=720 plane-id=31 connector-id=39

I measured those 16 signal wires, and it's not correct. VOUT0-D16~VOUT0-D19 have no signal

how should the next step be to debug the format of bt1120????

We have not tested BT1120 on our platforms and I do not have any further updates for you.

Regards,

Krunal