Tool/software:

Hi experts,

Sorry for the beginner question.

Please tell me why eMMC's DDR50 is limited to 48MB/s. Theoretically, isn't "48MHz * 8bit * 2(DDR) = 96MB/s"?

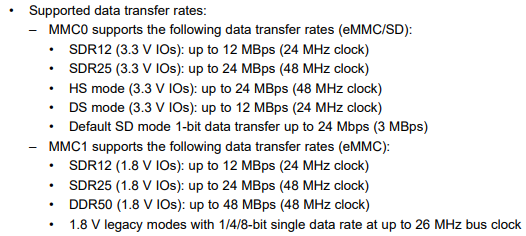

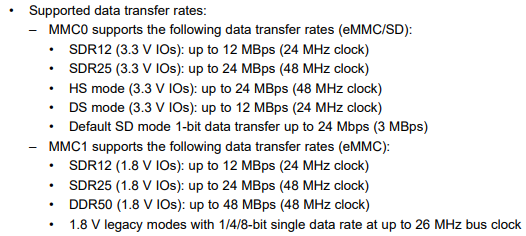

K2G eMMC v4.5 [TRM:11.12.1.1 MMC Features]

Best regards,

O.H

Tool/software:

Hi experts,

Sorry for the beginner question.

Please tell me why eMMC's DDR50 is limited to 48MB/s. Theoretically, isn't "48MHz * 8bit * 2(DDR) = 96MB/s"?

K2G eMMC v4.5 [TRM:11.12.1.1 MMC Features]

Best regards,

O.H

Hello,

Please refer to the following wiki

https://en.wikipedia.org/wiki/SD_card#UHS-I

In short, the speed is calculated as: 48MHz (Freq) * 4 (# of data lines) * 2 (DDR) = 384Mbps / 8 = 48MBps.

Regards,

Prashant

Hello Prashant,

Sorry, I accidentally pressed Resolved.

Thank you for your reply. The target this time is eMMC.

eMMC has 8 data lines, while SD cards have 4 data lines. Therefore, we understand that SD card is 48MB/s, but eMMC is 96MB/s.

48MHz * 8 (# of data lines) * 2(DDR) = 768Mbps / 8 = 96MB/s

Please let me know if there are any restrictions on eMMC, such as the number of data lines being limited to 4 during DDR operation.

Best regards,

O.H

Hello,

I see I mistakenly aligned MMC1 with SD card and accordingly calculated the speed.

Let me check with the expert on your query and get back to you.

Regards,

Prashant

It appears the person creating this content for the TRM did not understand the data transfer mode names defined in the eMMC and SD Card standards. They used names that can be confusing to those that are familiar with the names used in the standards.

Which port are you planning to use for the eMMC device? Note: The MMC0 port only supports 3.3V and the MMC2 port only supports 1.8V. You may also need to consider which ports are supported by the eMMC boot code if you plan to boot form the eMMC device. I will try to clarify the data transfer speeds supported once you tell me which port is being used.

Regards,

Paul

Hello Paul,

Thank you for your supports.

Which port are you planning to use for the eMMC device?

We plan to connect it to MMC1 (I/O: 1.8V) with 8 data lines.

You may also need to consider which ports are supported by the eMMC boot code if you plan to boot form the eMMC device.

Is it possible to boot from an eMMC connected to an MMC (not limited to MMC1)?

None of the threads below seem to be able to boot in the end.

Best regards,

O.H

My replies are based only the information found in the device TRM and datasheet since I was not involved in the development of 66AK2G12.

My previous comment about booting from eMMC was not based on any specific device knowledge. It was simply a generic warning where I was suggesting you research the device boot capabilities before deciding which port to use. I had not reviewed the eMMC boot information in the TRM before sending my previous reply. After reviewing the Initialization chapter in the TRM today, it appears the device supports booting from an eMMC device on either port.

The datasheet Feature List seems to contain a better definition of the data transfer speeds supported than the information provided in the in TRM.

Based on the datasheet, the device supports any of the following three eMMC data transfer speed modes.

Note: the maximum frequency defined for this port is 48MHz, but your system designer must perform a timing analysis that includes the impact of PCB delays and the output delays of each device (66AK2G12 and eMMC) on the setup and hold requirements of each device to ensure there is enough timing margin. It may be necessary to reduce the operating frequency to a value that is less than the max frequency to provide enough timing margin.

Regards,

Paul

Hello Paul,

Thank you for your reply.

The datasheet Feature List seems to contain a better definition of the data transfer speeds supported than the information provided in the in TRM.

Based on the datasheet, the device supports any of the following three eMMC data transfer speed modes.

Note: the maximum frequency defined for this port is 48MHz, but your system designer must perform a timing analysis that includes the impact of PCB delays and the output delays of each device (66AK2G12 and eMMC) on the setup and hold requirements of each device to ensure there is enough timing margin. It may be necessary to reduce the operating frequency to a value that is less than the max frequency to provide enough timing margin.

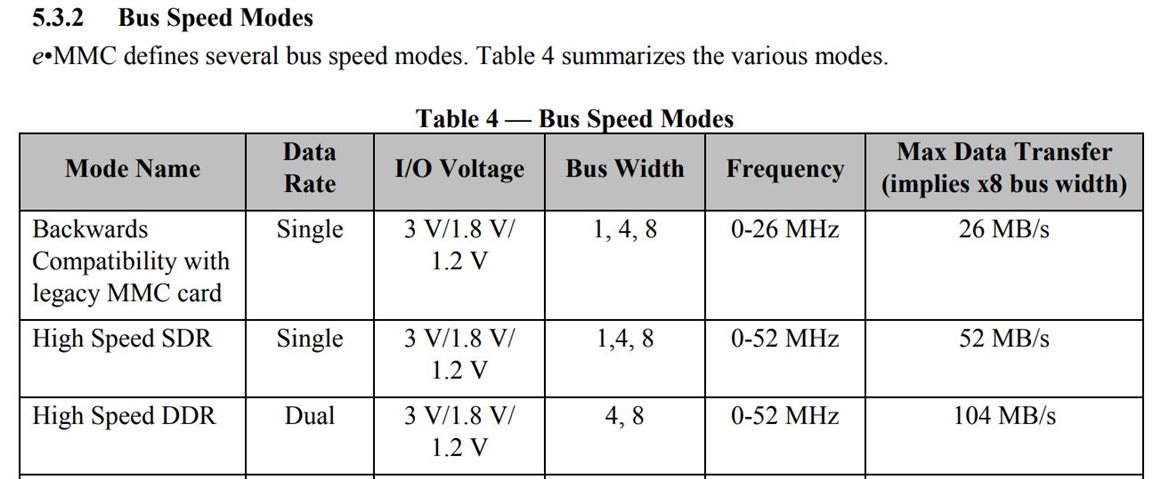

In other words, the 66AK2G12 eMMC can use "High Speed DDR" mode, and the theoretical value is as follows:

48MHz * 8 (# of data lines) * 2(DDR) = 768Mbps / 8 = 96MB/s

However, whether it can be used according to the theoretical value depends on the system designer's sufficient verification and judgment.

Is that right?

After reviewing the Initialization chapter in the TRM today, it appears the device supports booting from an eMMC device on either port.

Could you please confirm again from the perspective of hardware and software whether K2G can boot eMMC?

We have confirmed the contents of the TRM, and it appears that booting from eMMC is possible.

However, the problem with U-boot and the BOOTMODE pin has not been resolved, and we have not found any cases where booting has been possible.

In particular, this thread:e2e.ti.com/.../66ak2g12-evmk2gx-emmc-boot-support-66ak2g12-emmc-boot-support

Best regards,

O.H

That is the theoretical data transfer rate during actual read/write operations. It does not represent a constant throughput. The actual data rate will have other dependencies like bus turnarounds between read and write operations, and other protocol overhead associated with data transfers. There may also be potential bandwidth limits inside the 66AK2G12 and attached eMMC devices, which includes system specific software overhead that needs to be considered. The software team may have performance benchmarks that would be a better indicator of expected data throughput.

I do not have enough knowledge of the device or experience supporting this device to confirm it supports booting from eMMC. As you pointed out, a few customers have encountered problems getting eMMC boot to work. However, the TRM clearly indicates it is supported. We do not know how many customers were able to successful boot from eMMC. I can send a few internal emails to see if anyone has more information on this topic.

Regards,

Paul

Hello Paul,

Thank you for your reply.

The software team may have performance benchmarks that would be a better indicator of expected data throughput.

Could you please confirm whether there are any benchmarks?

I can send a few internal emails to see if anyone has more information on this topic.

Could you also email this to a members?

Best regards,

O.H

EMMC SW driver performance is documented here:

software-dl.ti.com/.../Release_Specific_Performance_Guide.html

Hi Paul,

Thank you for the information.

Q:Is it correct that, in the range tested with TI's SDK, the maximum speed is 43.46MB/s, the theoretical value on the device (hardware) side is 96MB/s?

Looking at "AM57XX-EVM", when using EXT4, Read is up to 79.97MB/s.(Write is ignored as it is caused by the file system.)

Since AM57x supports "High Speed DDR" with MMC2(eMMC), the performance value is 96MB/s when operating at 48MHz, which makes sense.

However, "K2G-EVM" has a maximum Read speed of 43.46MB/s when using EXT4.

This seems to be 48MB/s (4bit), so I'm confused. If there is a theoretical limit of 48MB/s on the device side, please let me know.

Also, could you please follow up on whether booting with eMMC is possible?

Best regards,

O.H

O.H,

eMMC boot on K2GEVM is supported. At SoC level, customers need to check TRM, datasheet and Errata and test this boot on their custom board before placing production flash orders.

Thanks and Regards,

Rahul

Hi Rahul Prabhu,

Thank you for your support.

eMMC boot on K2GEVM is supported. At SoC level, customers need to check TRM, datasheet and Errata and test this boot on their custom board before placing production flash orders.

I understood that, regarding eMMC boot, the hardware is supported, but the only way to check the software (u-boot) support is to check it on the actual device based on the existing information.

Q:Is it correct that, in the range tested with TI's SDK, the maximum speed is 43.46MB/s, the theoretical value on the device (hardware) side is 96MB/s?

Is it correct to say that there is no way to check the above other than to verify it on the actual device?

Best regards,

O.H

Is it correct to say that there is no way to check the above other than to verify it on the actual device?

there is currently no active development on this device so beyond the resources I have shared there is no way TI can check to verify this on the actual device