Tool/software:

Hello, TI:

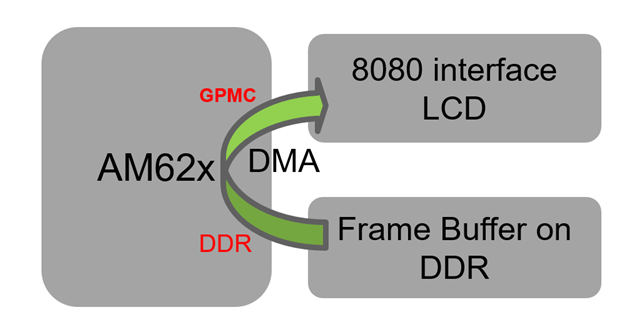

We currently have a requirement to use GPMC to connect to an LCD with an 8080 interface (8-Bits data), and control commands and data through an address line A20. The display driver is a self-written fb driver.

I have a question to ask. If the fb video memory writes 1 byte of data to the GPMC, I want to use the BCDMA method to send the 1024 bytes of data in the video memory fb to the GPMC peripheral using the DMA_MEM_TO_DEV method, and the GPMC sends it to the LCD. This usage scenario should be achievable on the AM62x platform at present?

Please ask TI experts to help reply. There is relatively little information on this aspect of AM62x.