Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

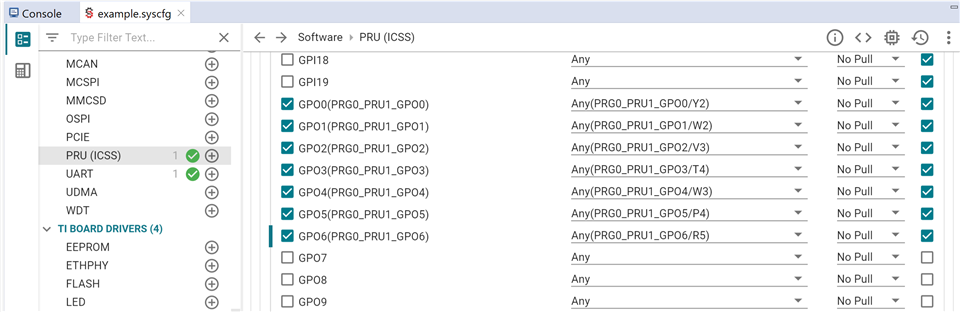

Each PRU_ICSSG PRU processor implements fast GPO through its R30 register and fast GPI through R31 register. AM64x/AM243x has 20 pinned out PRU GPIO pins and the device multiplexes all GPI signals and their corresponding GPO signals onto the same pin using different multiplexing modes.

How to switch between GPO and GPI operation from PRU firmware code?