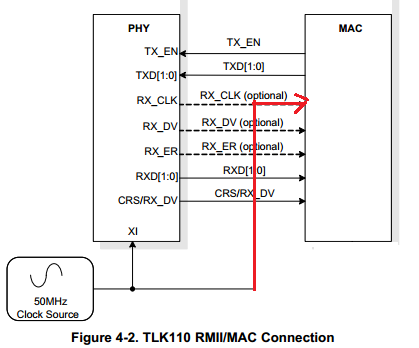

Do you have an example design of AM335x connected to a 10/100 Phy using RMII interface. What I am wondering is whether the Phy or the CPU is supossed to provide the 50MHz clock. Advisory 1.0.16 in the AM335x Errata states that its output clock doesn’t comply with requirements of external RMII phy.

Will this be fixed in Rev 2 silicon?