Hello,

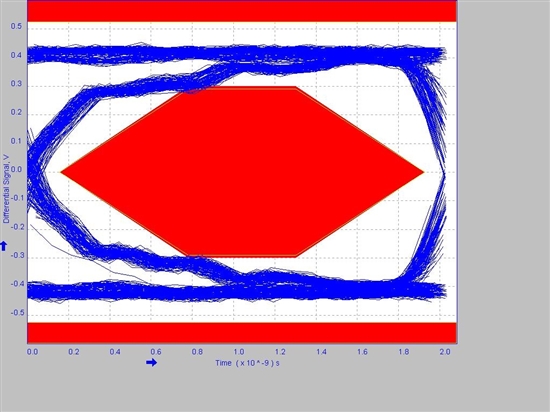

we developed a module using AM3352. The USB outputs are routed as differential pairs with correct differential impedance of 90Ohms and roughly 45 Ohms single ended. When envoking USB test modes and checking on a fast digital scope we find that the eye pattern does not meet USB2.0 high speed requirements. Additional ESD protection was already removed. The silicon used is still first revision, we are currently trying to repeat the measurement on BeagleBone Black which is using newer revision of the chip.

Has Texas Instruments ever verified USB compliance on physical layer by measuring eye pattern ?

Is there anything that can be done to boost the signal i.e. increase slew rate ? We don´t see such options although we have access to the documents that are only available under NDA.

We know there is a bug on first silicon related to USB but this appears to be a different issue

since our module is already in mass production this is a serious problem for us

thanks and regards, Christoph