Other Parts Discussed in Thread: CCSTUDIO

Hi All,

I am using custom DM8168 board and ezsdk_dm816x-evm_5_05_02_00 for software development, got the Ethernet PHY: GENERIC @ 0x18 on u-boot but ping does not happen. What could be the issue. Please find the ping log below:

serverip=192.168.1.100

ipaddr=192.168.1.101

netmask=255.255.255.0

TI8168_EVM#ping 192.168.1.100

Using DaVinci EMAC device

ping failed; host 192.168.1.100 is not alive

TI8168_EVM#

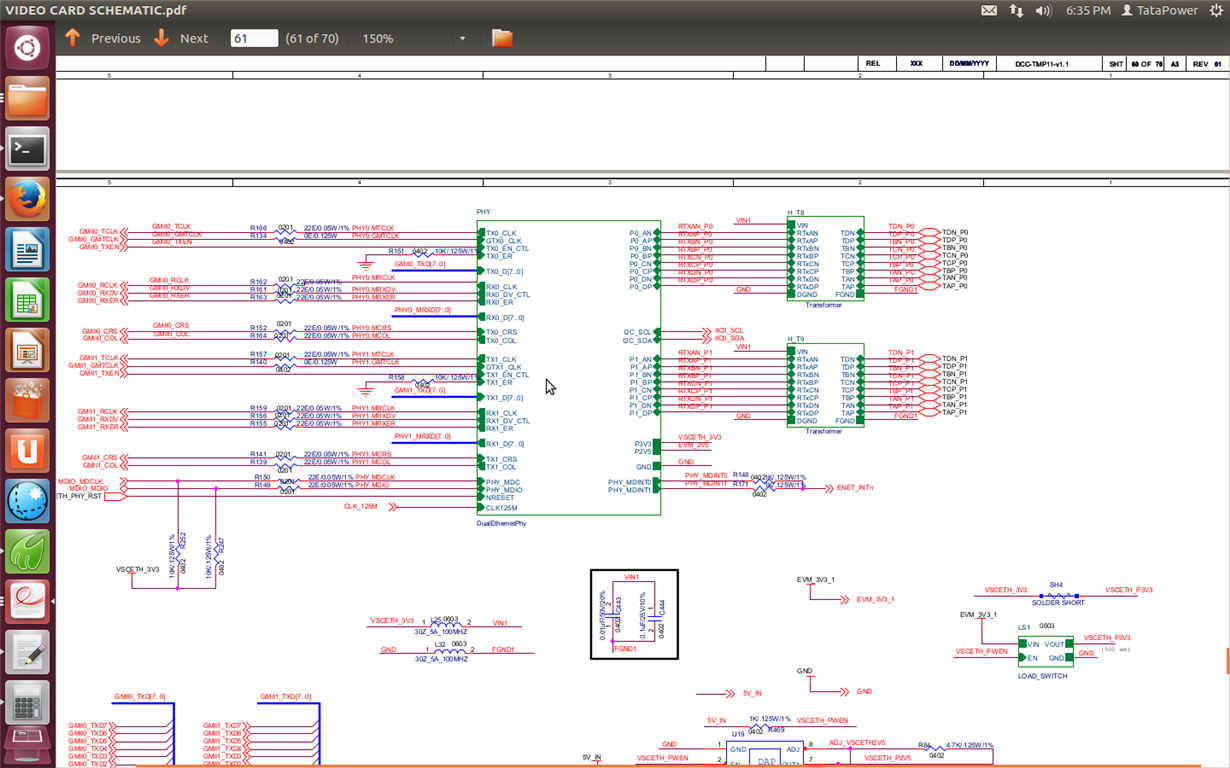

Using VSC8502 dual phy using in the board and please find the attached design.

Please help us to resolve the issue.

Thanks,