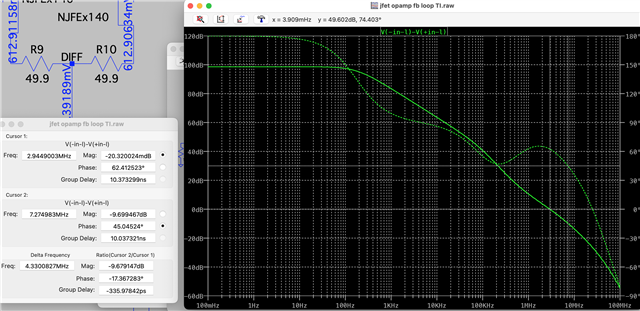

Other Parts Discussed in Thread: OPA604, OPA202, LME49860, TINA-TI

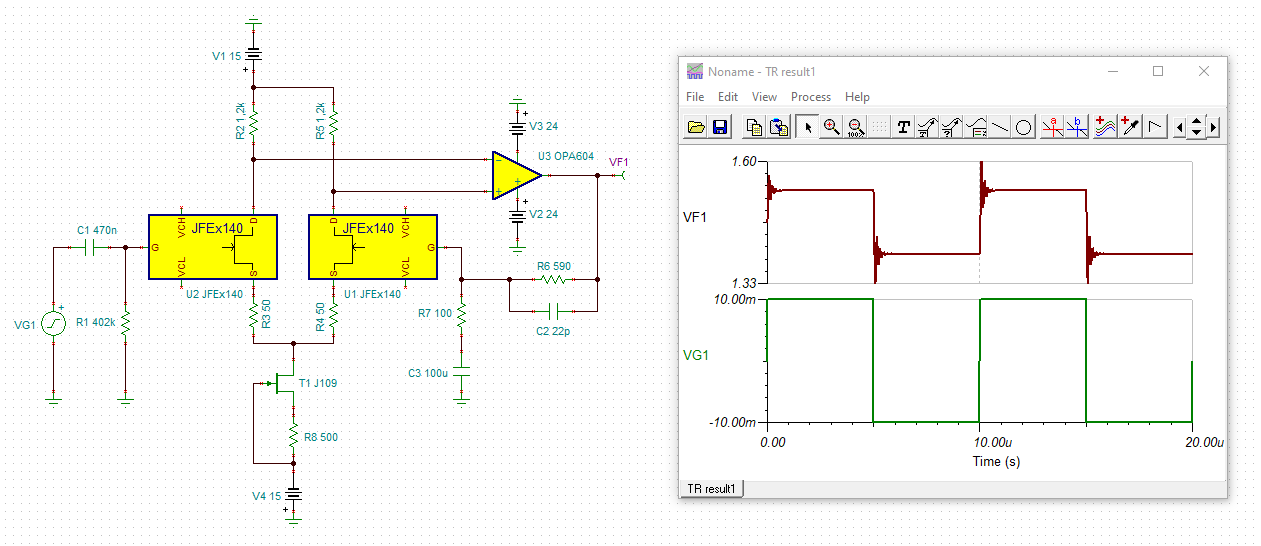

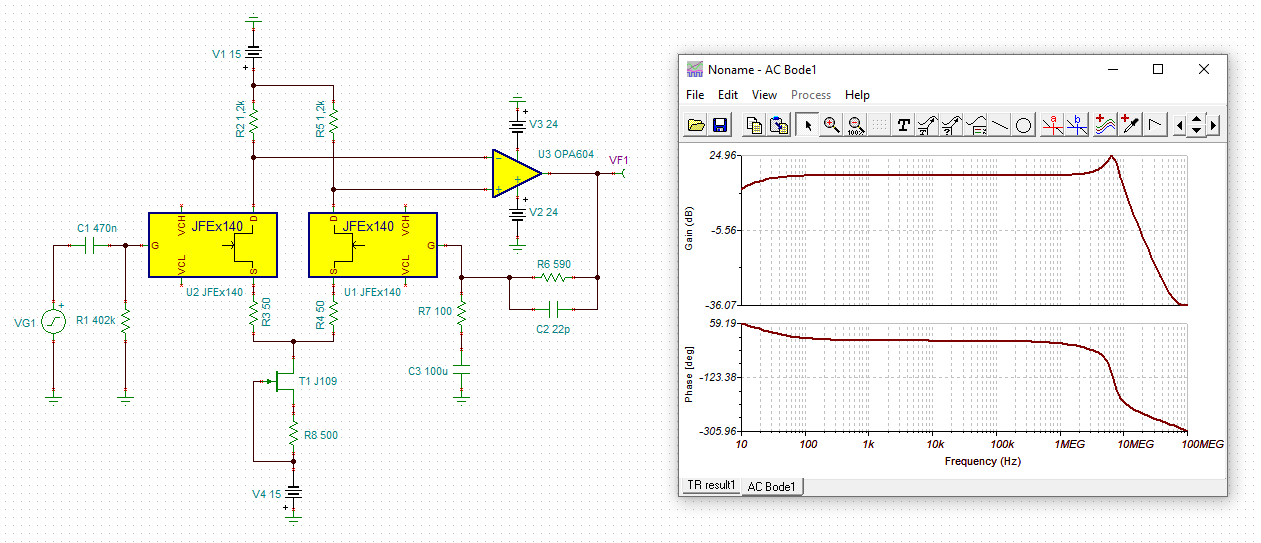

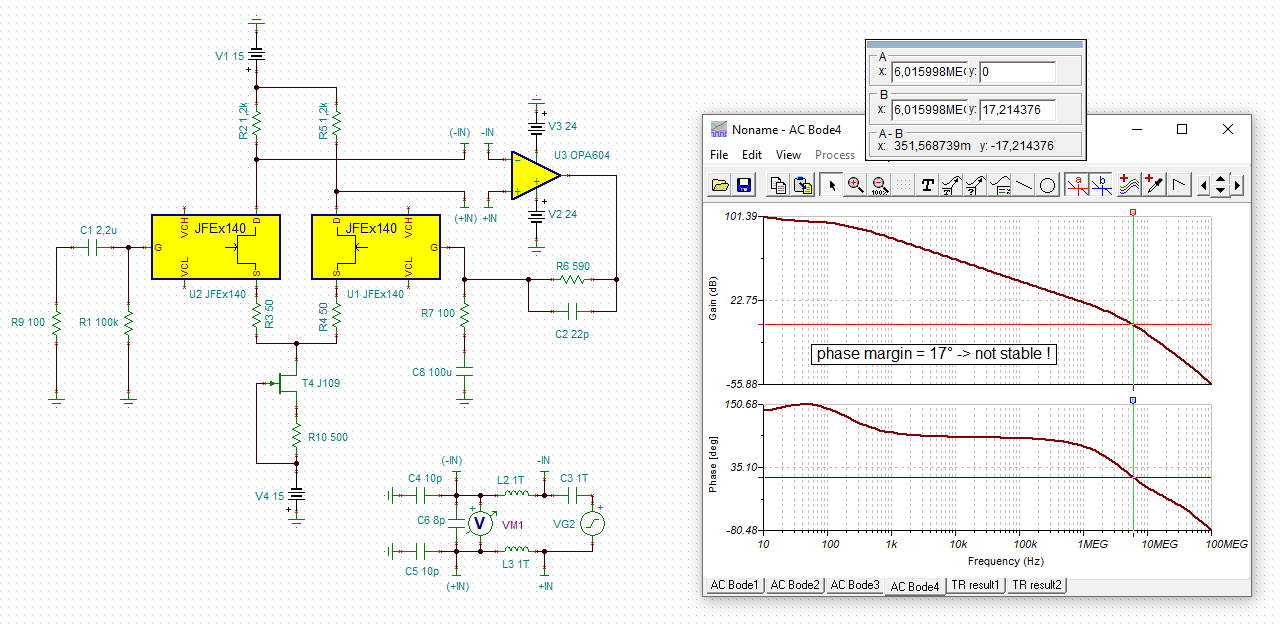

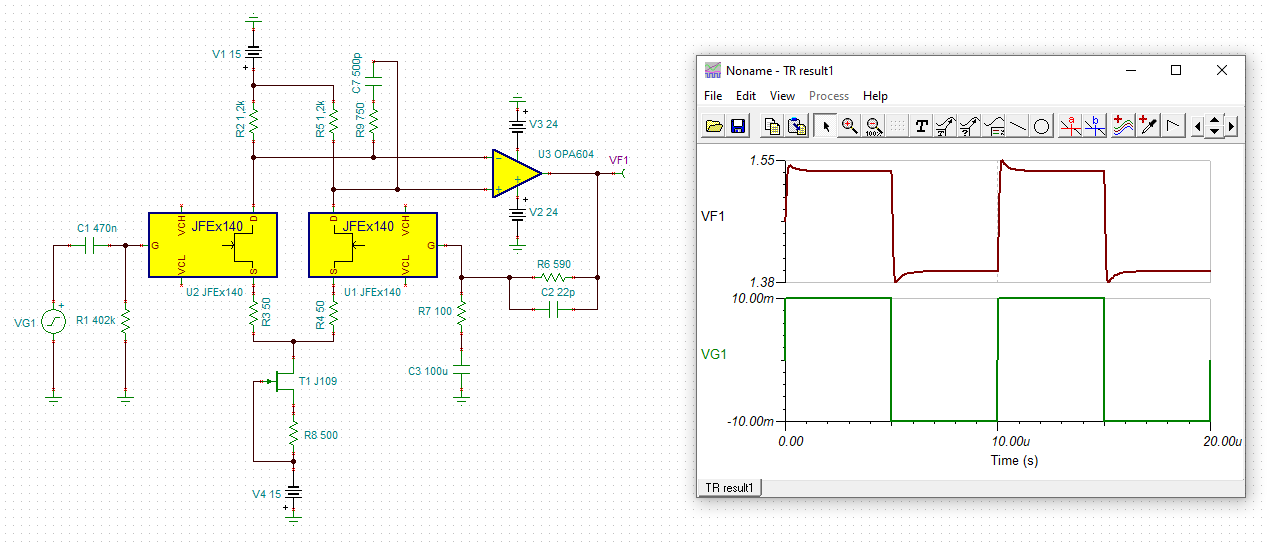

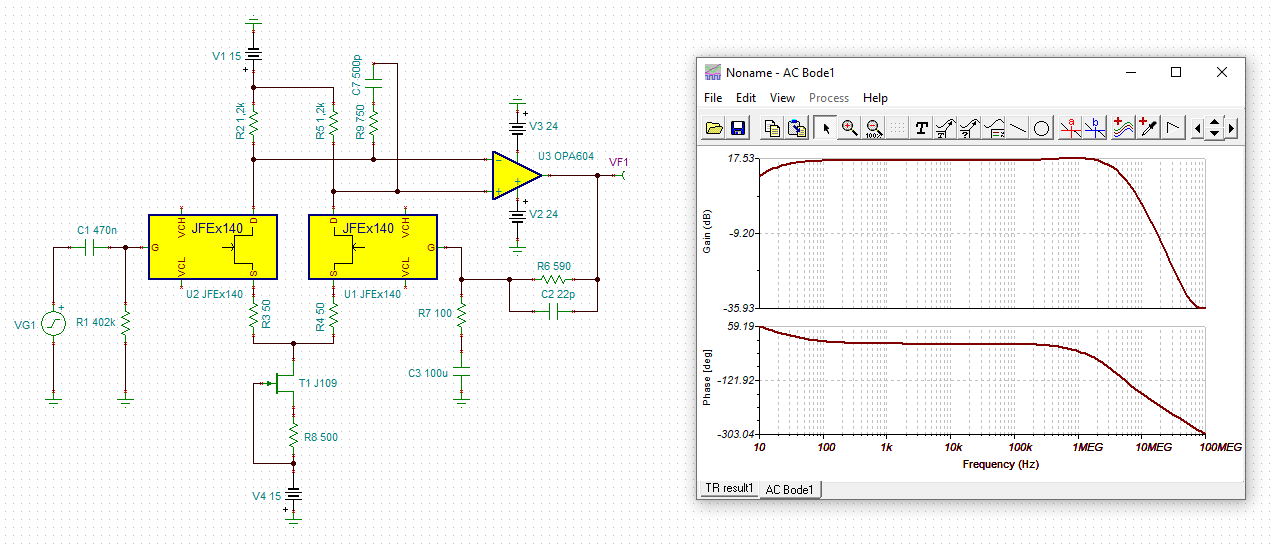

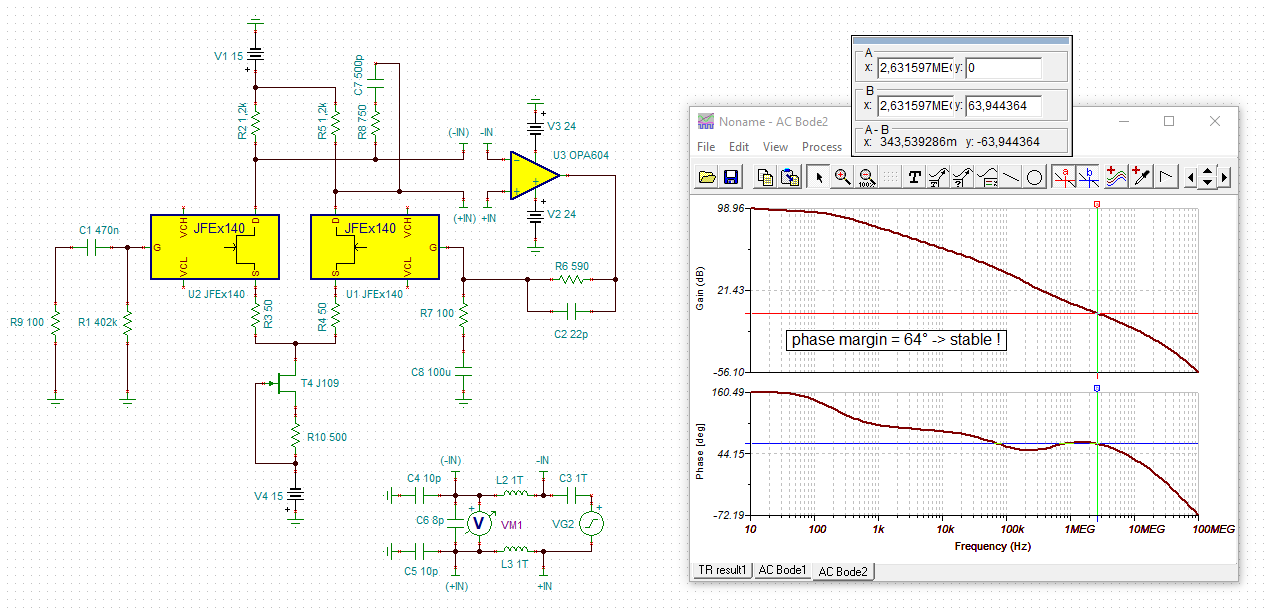

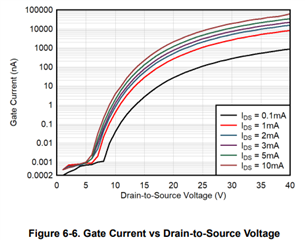

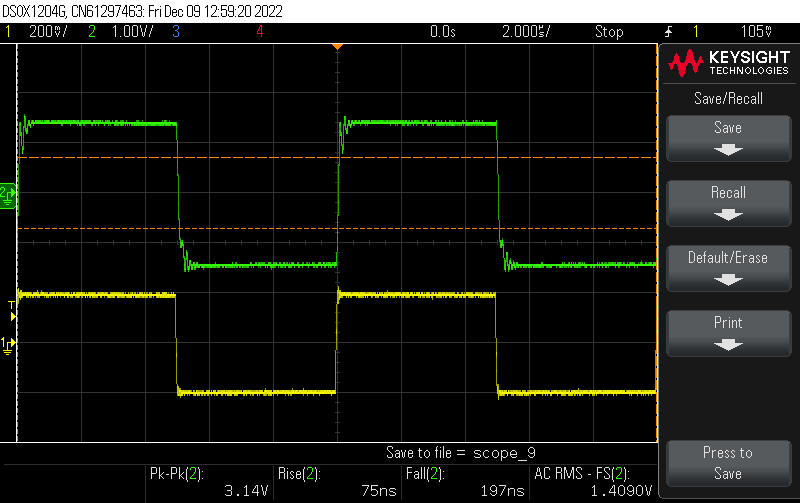

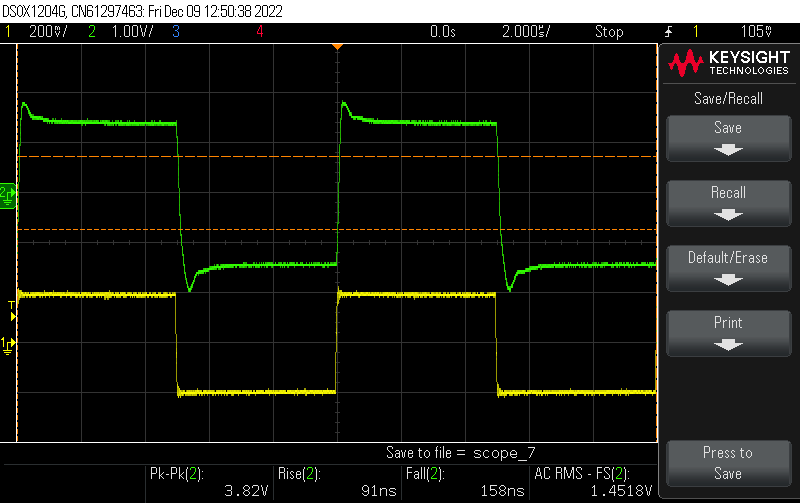

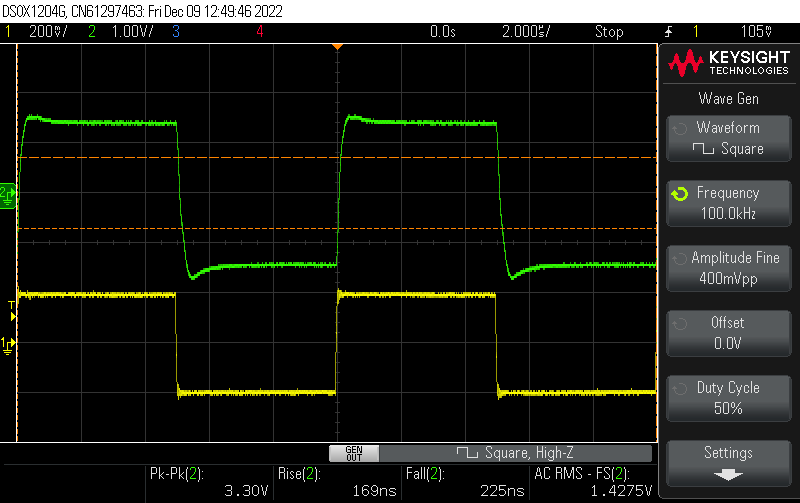

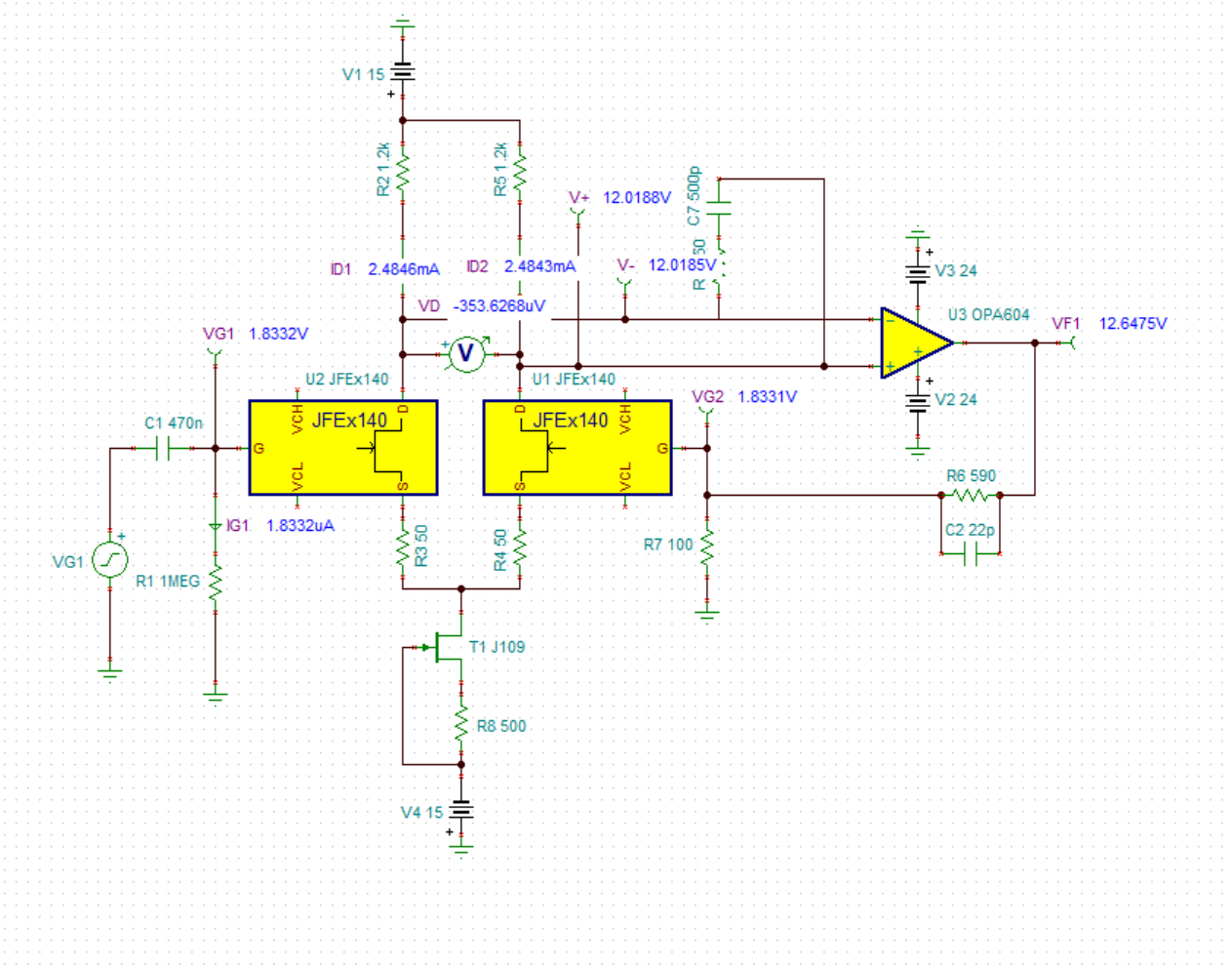

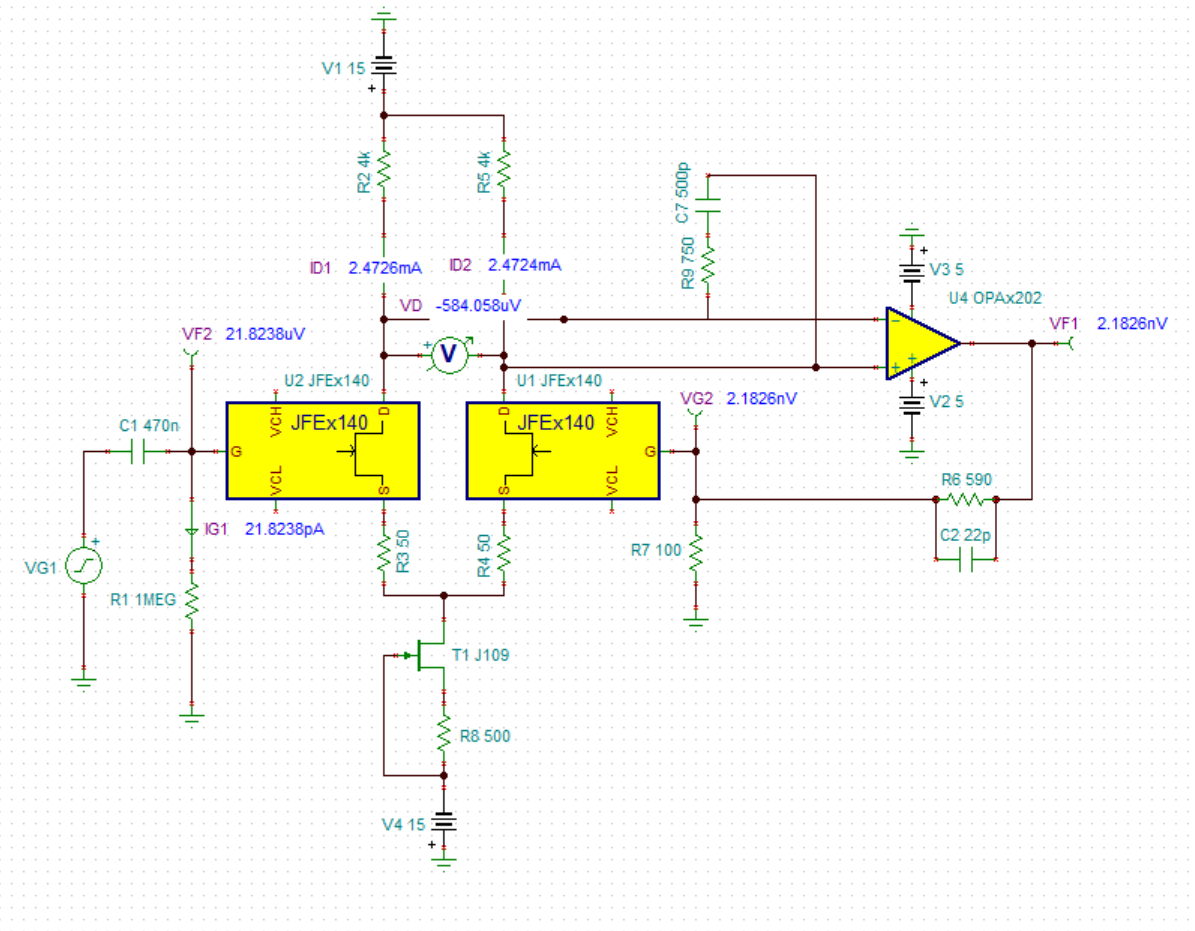

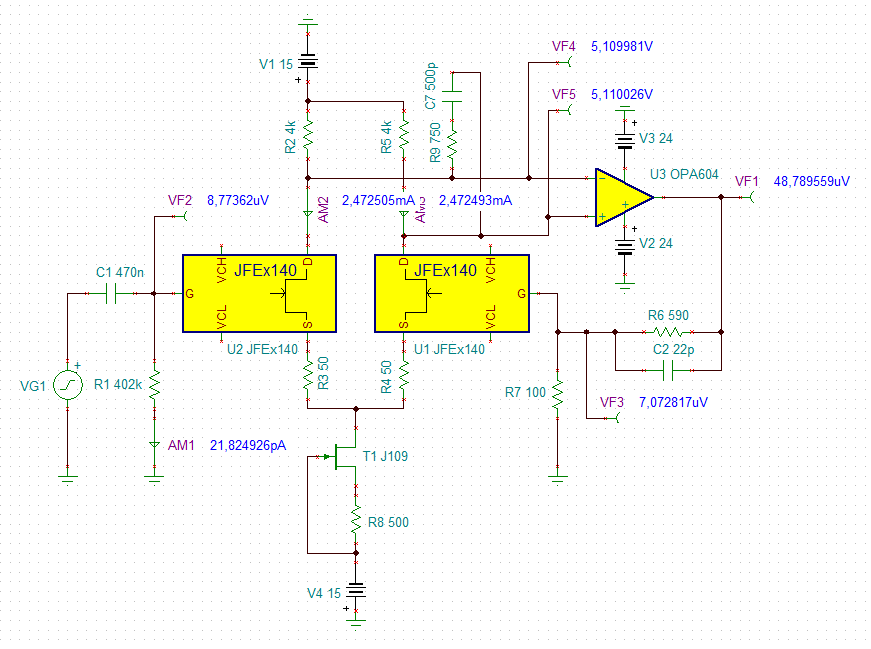

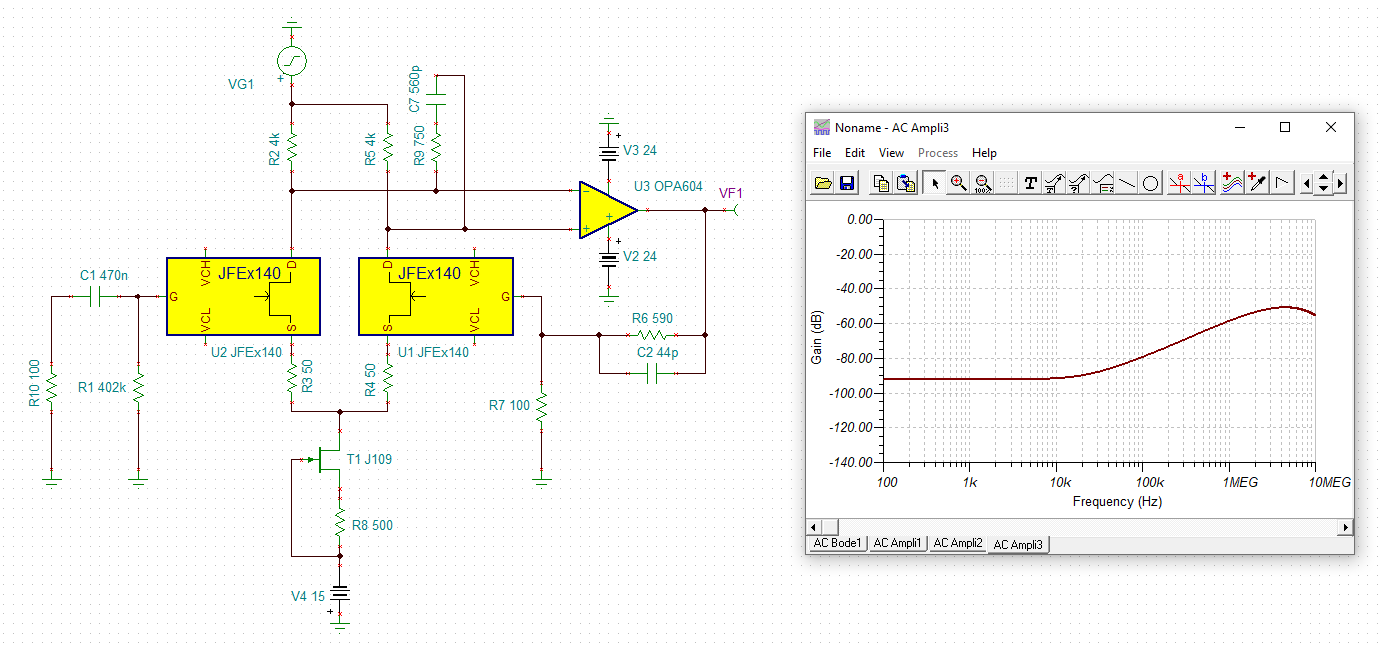

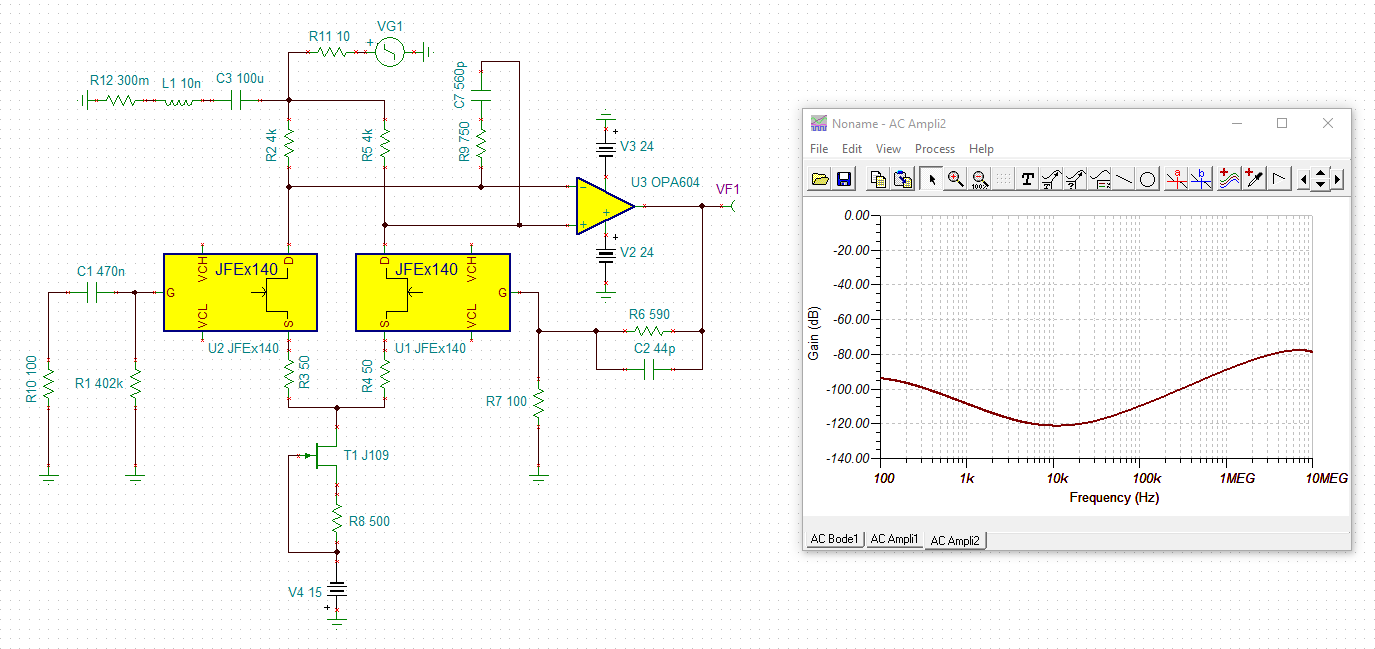

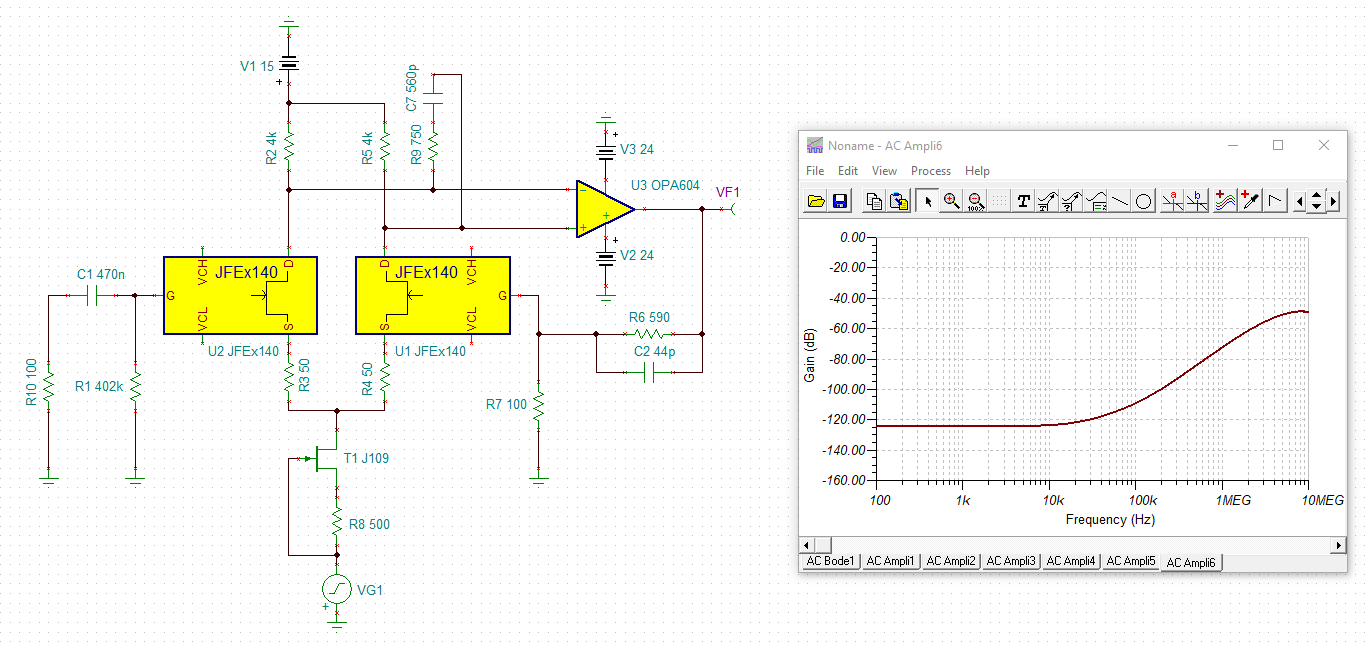

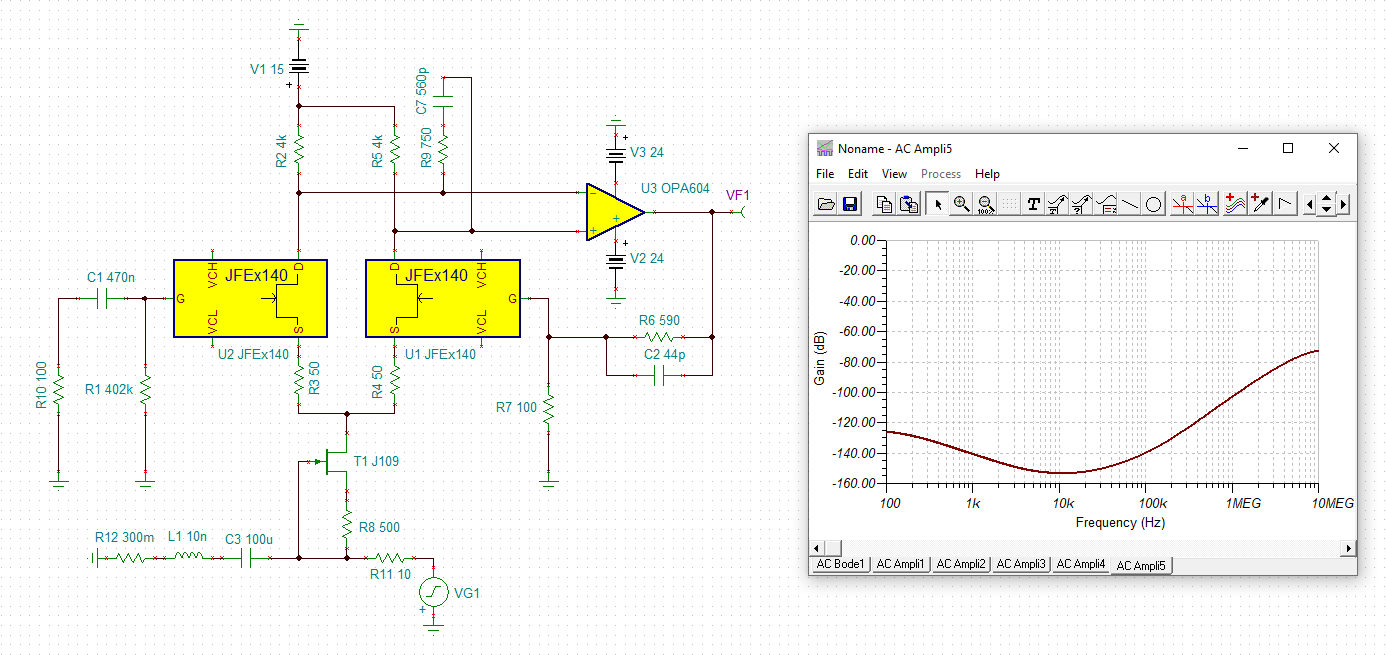

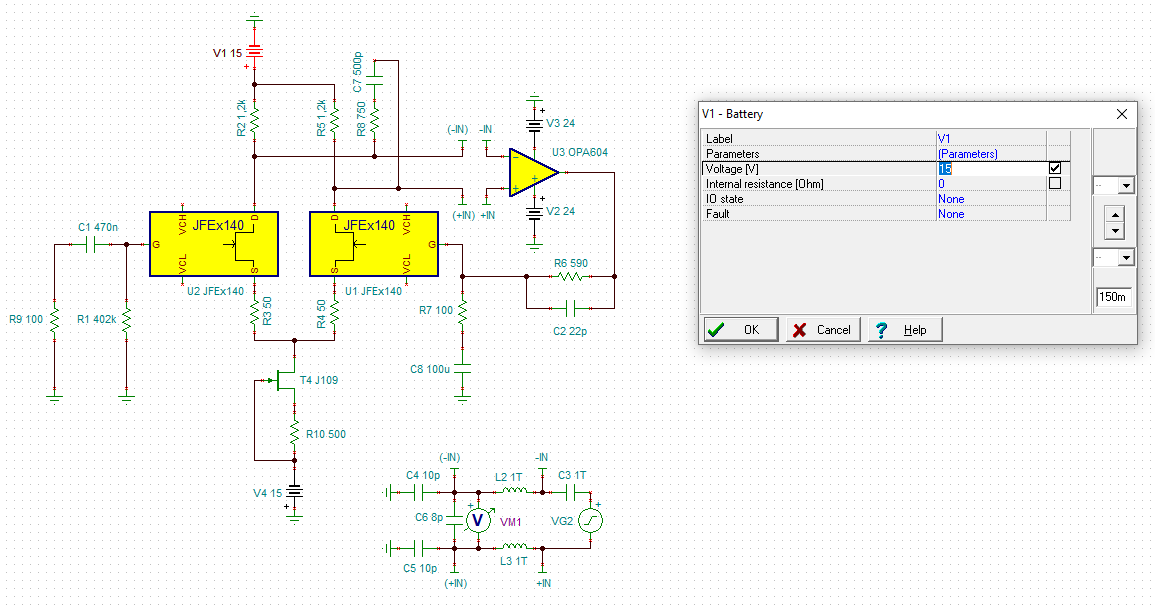

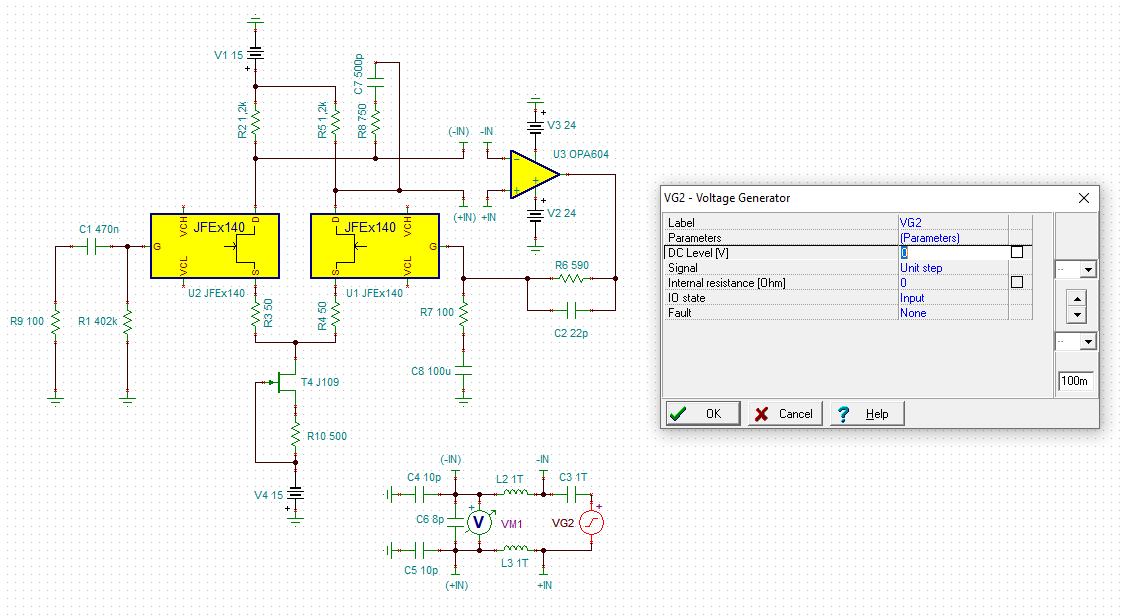

I've built a composite amplifier using a JFE2140 dual JFET and a OPA604, similar to Fig. 9-6 on the JFE2140 DS. Two that I've built work fine, but two others exhibit DC gain. As the input is increased, the DC output goes positive. When I tested the first one that had this, I thought there must have been a wiring error I couldn't locate, until I built another with the same problem. I've exhausted my ability to troubleshoot these two problem samples. LTSpice does not show anything amiss. (I don't believe PSPICE-TI supports my Mac OS, but please let me know if it does.)

The total gain should be about 7, and I have an input blocking cap, so that the only DC at the input of the first JFET gate should be due mostly to imbalance in the circuit. By the time the input AC signal is 1 volt RMS, there's more than a volt of offset at the output, however. 1.75V peak at the input signal results in 5.4V DC output.

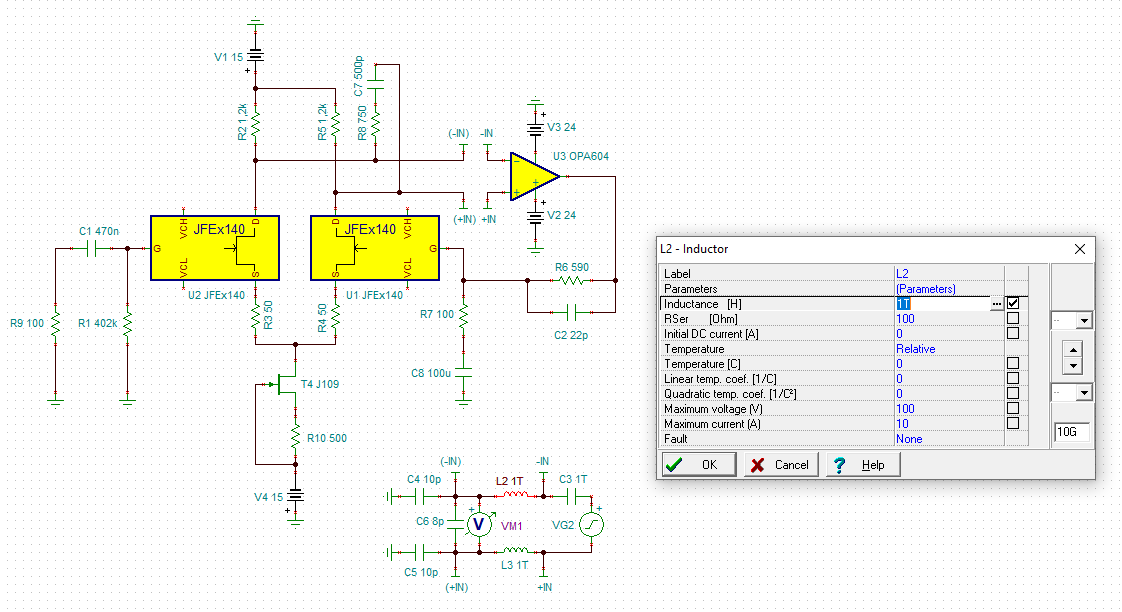

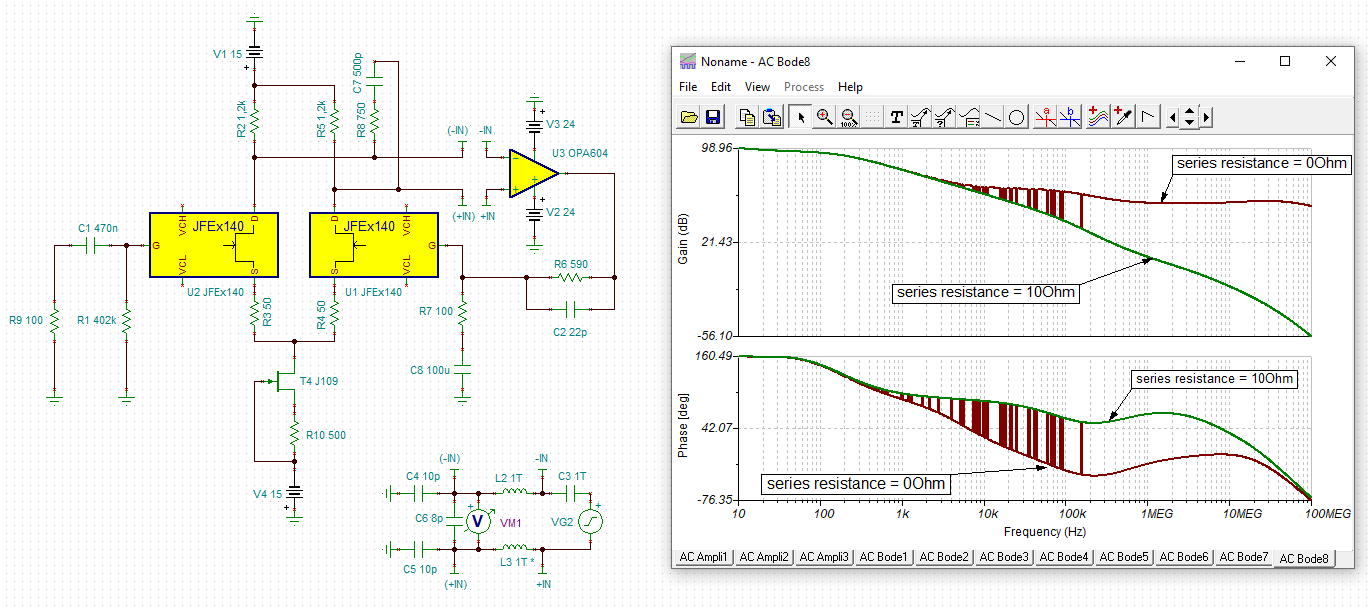

A schematic follows.

What am I missing? Thanks in advance.

jfet opamp fb.pdf