Other Parts Discussed in Thread: OPA2196, OPA192, TINA-TI, ADS7046, ADS8860, OPA320, OPA328, OPA625

Hi,

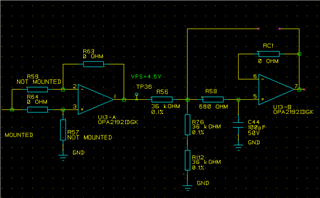

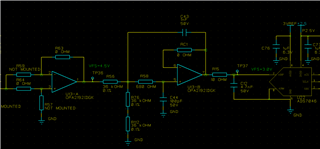

we have the above opamp configuration to measure the DC-link voltage in our frequency converter for maritime applications (800kW to 6MW power range). (Ahead of this circuit there is a high voltage voltage divider not shown). The opamp is powered from a single supply rail (GND to +15V). We want to be able to measure voltages close to 0V. I have selected the OPA2192 for its "beyond the rails" performance. (The voltage divider R56+R76+R112 is there for legacy reasons, we had a 5V ADC in the design previously). When I feed this circuit with 0V input, I measure 0.6mV at the output of the U13-A amplifier (buffer). At the output of the U13-B amplifier (filter), I get 19.3mV. This is quite a lot more than I expected. If I remove capacitors C43 and C44, I get 3.1mV at the output of U13-B. This is more in line with what I was expecting. The input bias current into U13-B.5 is supposed to be 5-20pA. At 20pA and 36k||72k=24k impedance it should be 0.48uV(?) Why is there less bias current with no capacitors?

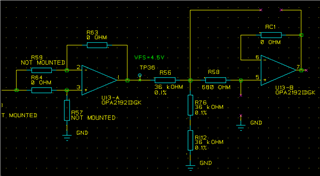

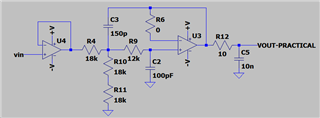

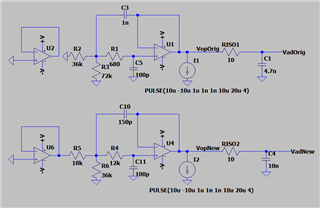

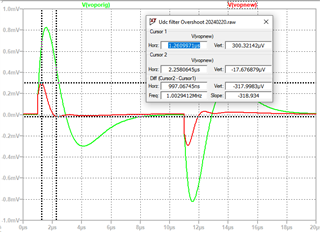

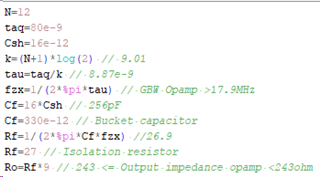

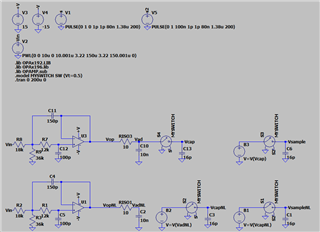

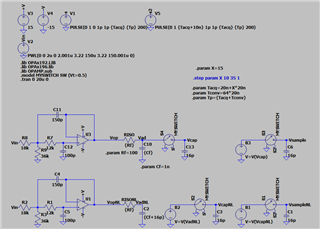

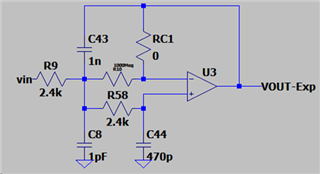

As an experiment, I did a redesign of the filter stage to lower the resistances like this:

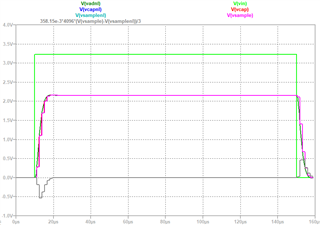

The result is that I get 0.8mV at the output of the buffer stage and 5.9mV at the output of the filter stage (success).

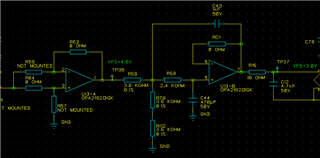

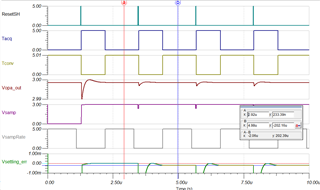

It seems that the bias current of the filter amplifier is something like this for my circuit and 0V input voltage:

Original circuit: (19.3mV-0.6mV)/(24kohm+680ohm)=0.76uA

Modified (lower resistance) circuit: (5.9mV-0.8mV)/4.8kohm=1.062uA

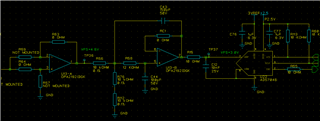

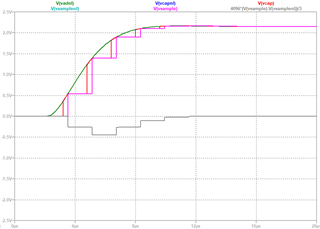

I see that you have a graph of the input bias current vs common mode voltage in figure 18 in the datasheet. The graph only shows the middle of the common mode range.

How does the input bias current change close to the negative rail?

(PS: We will probably change the design to use the OPA2196 due to availability and cost. I get similar results with that part as well)