Other Parts Discussed in Thread: EK-TM4C1294XL, TMS320F280049C, TMCS1101

Hello,

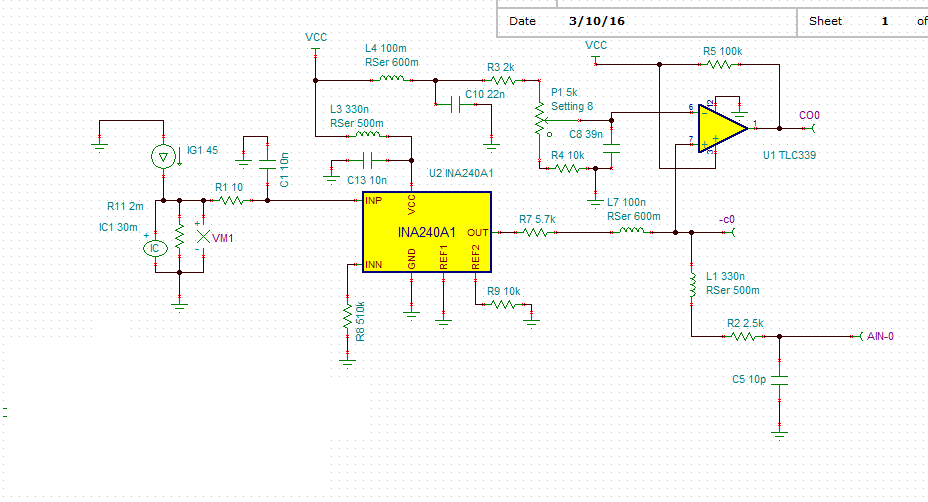

Recently did new experiment with small Nidec 12 pole motor and three 240A1's, REF1/2 mid supply (1.65v), VS=3.34v. Contrast REF1/2=GND all three 240's on a separate sub PCB sit just above shunt in both experiments. The three sub PCB grounds separated individual wire feed into the target MCU ground plane isolated from shunt ground.

The ADC conversion values per millivolt for the same amount of current load in each experiment differed greatly. The 1.65v mid supply flat lined at 1.6 amps increased maybe 100mA upon adding any amount off additional current load. Yet the experiment where REF1/2=GND the output rose 1.6A and upon adding current load the ADC samples easily traverse past 2.1 amps. In each experiment the single ended ADC channels and conversion scale factor 0-4096 was configured to show steady state near 1.6A.

The main difference being first experiment ADC incremented from 0.1,.2,.3.4,.5,.6,.7,.8,.9 etc. up to 1.6A and the second (REF=mid supply) jumped to 1.6A skipping over all lower values. The ADC conversion calibration was derived from the Nidec motors run time steady state load current in both experiments. What happened to the open loop linearity in the second experiment?

There seems to be an issue that output open loop linearity divides in half for REF set mid supply (1.65v) thus affecting ADC granularity near scale 2048. How can this be occurring in the ADC when the full scale is 4096 in each experiment? Is there some kind of counter measure inside some TI ADC modules expecting a division in open loop output linearity analog signals fixed to a 1.65v threshold? Perhaps analog converters require band gap (1.65v) to maintain bidirectional REF open loop output linearity? Seemingly that is not required in unidirectional REF configurations such that INA output maintains full scale (4096) open loop linearity.