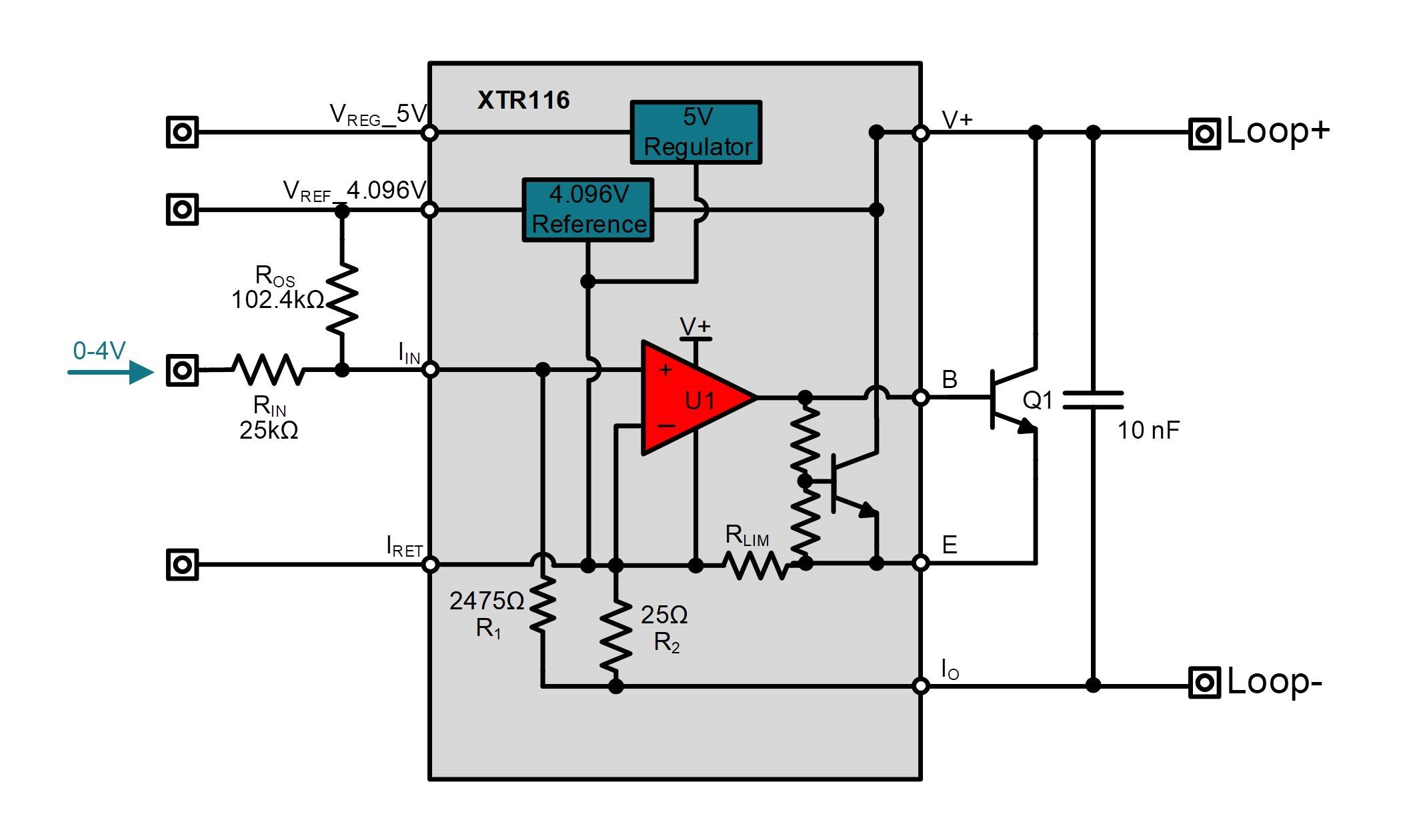

Other Parts Discussed in Thread: XTR116

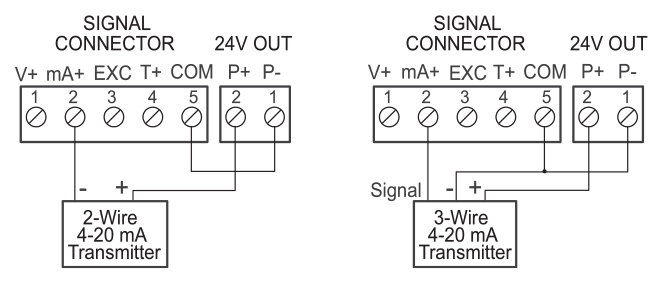

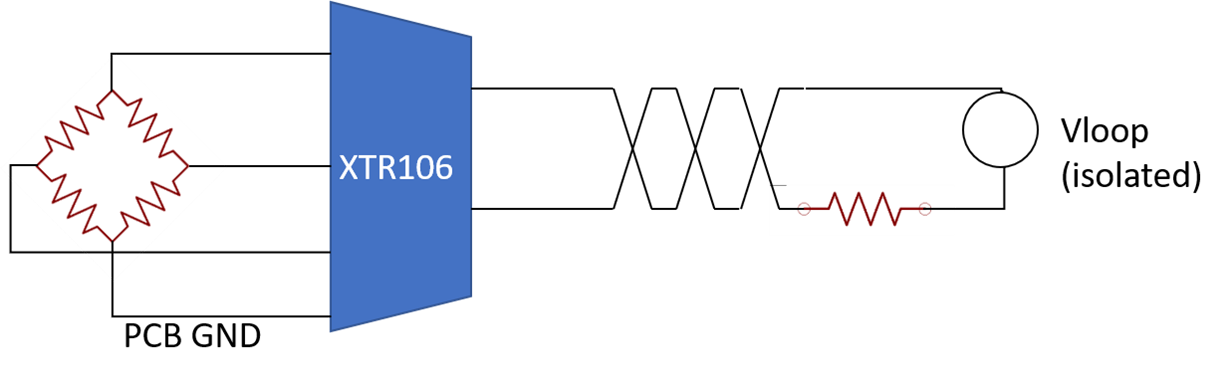

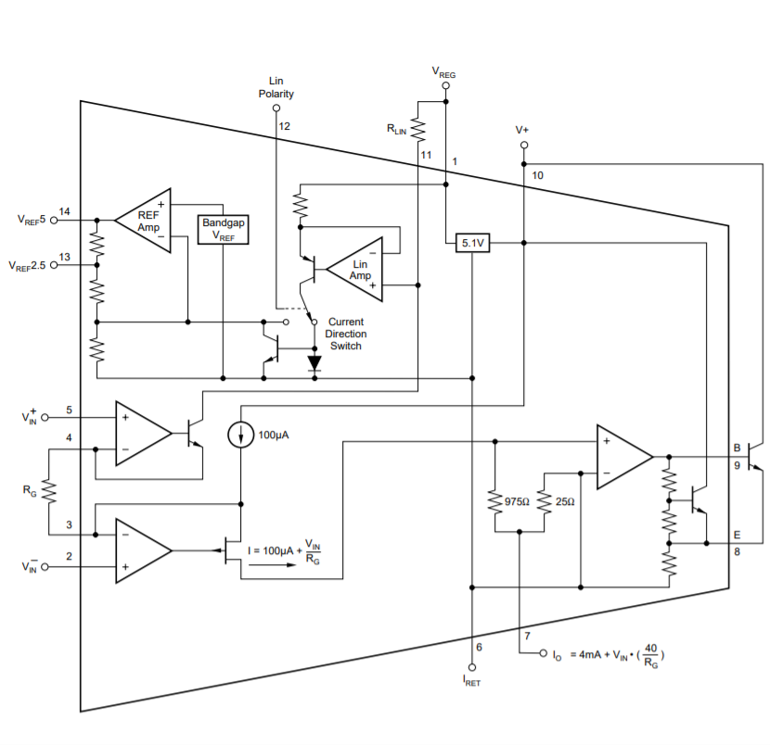

I have a case where I have two full bridge sensors, and the EXC- legs are tied together. The voltage outputs of the 4-20mA readouts are commonly isolated for UL safety reasons, so the negative terminals are floating with respect to each other, and to earth ground. In this case, is it possible to tie the Iret pins of the two XTR106s together? From reading this blog post, it does seem like it will be okay if Vloop- is not assumed to be ground.

Thanks,

Paul