- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi

I have a 3.3V OSC and I want to feed the CDCVF2310PW from this OSC (at its "CLK" pin).

However, the target FPGAs which require the clock are working at 2.5V and therefore I want to feed the CDCVF2310PW driver from Vdd=2.5V.

My question is what is the maximum allowed voltage level at the CDCVF "CLK" pin?

In the data sheet I saw from one hand that Vih_min is 1.7V and there is no MAX but Vi (input voltage) is limited by Vdd (2.5V), so it seems as it is not proper design to feed a 3.3V clock into a 2.5V CDCVF , true?

Any suggestions how to bypass this problem (OSC Vdd requires 3.3V and FPGA requires 2.5V input clock) without changing my components?

Thanks

Amnon

Hi Amnon,

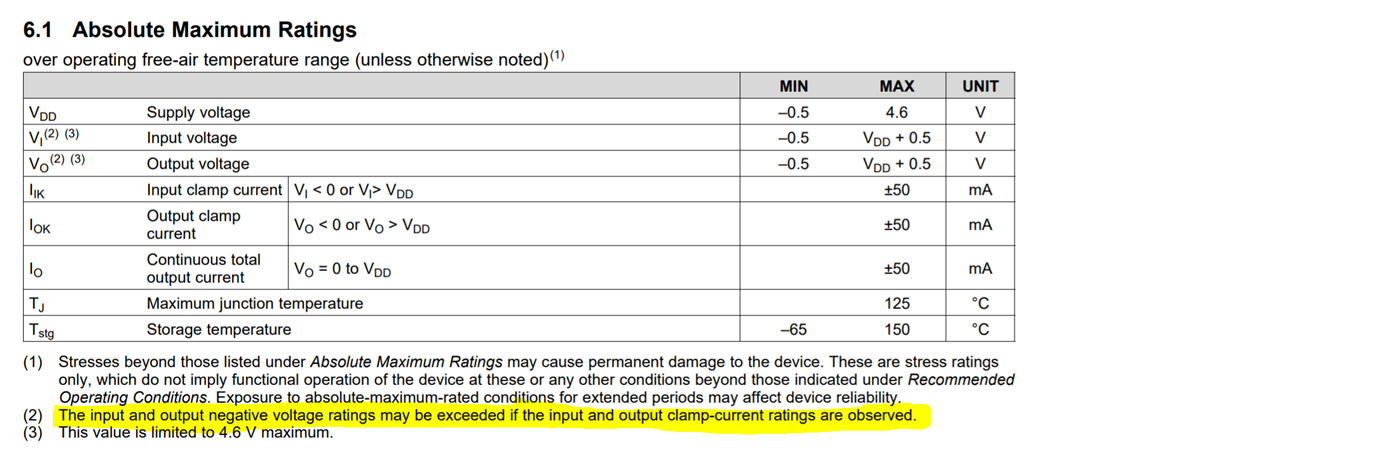

The absolute max Vi is VDD + 0.5, which is 3.0V in your case. Using a 3.3V OSC would violate this and potentially damage the device.

While you could proceed with the 3.3V OSC by taking into account of note 2 (see image below), you could alternatively use voltage dividers to reduce OSCin to the appropriate Vi range.

Regards,

Jennifer

Hi

Thanks for the prompt and elaborated answer.

I would like to verify on your answer:

1. In case I use a serial termination resistor of 33ohm between the OSC and the CDCVF, does it mean that I meet Note 2 ?

If not, how do I meet practically Note 2 (keep the Clamp current low enough) ?

2. I also thought about the voltage dividers (I found that resistors of 1.5K and 511 ohm can do the trick) but what about the RC affect, will it not "destroy" the Signal Integrity of the clock signal at the CDCVF "CLK" pin?

Thanks again

Amnon

Amnon,

1. The 33 ohm resistor would be not sufficient for the clamp current absolute max rating of +/- 50mA.

2. Use large resistors (greater than 1k ohms) for your voltage divider and the signal integrity will be okay.

Regards,

Jennifer