Hi,

The EVM works fine with the attached file settings, but the customer's board has an unstable PLL lock and outputs a slightly higher frequency (all 5 prototype PCBs are the same).

I monitored the R and N divider / 2 outputs from the MUX to investigate the cause.

The R divider / 2 output was normal, but the N divider / 2 has a slightly higher frequency (since N-div = 3.84MHz, the MUX out was originally 1.92MHz, but it was a 2.08MHz output).

I thought that the input level to the VCO was low and asked to raise the CP current by register setting, but it was already Max, so I could not solve it.

The power supply is an external regulated power supply (the same power supply as for EVM).

What's wrong? Do you have any advice for improvement?

The R divider is normal, so at least I think the REF IN is good.

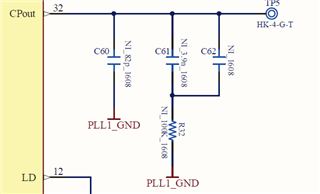

Is it a problem with the PCB layout?

Best regards,

Hiroshi