Other Parts Discussed in Thread: CDCLVC1108, CDCM6208

We are working at selecting an external clock source for the CLKIN inputs.

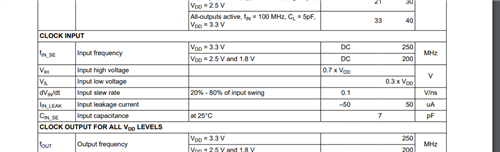

The datasheet only specifies the slew rate for the inputs (1~4V/ns)

Can I get an answer on the following parameters for the device please?

(For both CDCLVC1104 and CDCLVC1108)

1) The CLKIN signal voltage should be between GND ~ VDD and needs to meet VIH / VIL specs from section 6.3 right?

2) What voltage level is the slew rate (tr/tf) specified for? (20%~80%Vcc or 10%~90%Vcc?)

3) What is the max input capacitance of the CLKIN pin? (according to this E2E post typ is 2pF)

4) As long as the min pulse width (low and high pulse width) specified in 6.3 is met, does duty cycle matter? (45%~55% duty cycle limit, etc)

Regards,

Darren