Other Parts Discussed in Thread: LMX2594

Tool/software:

Hello,

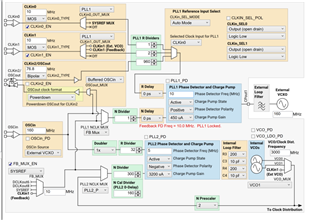

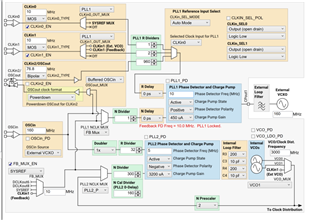

I am using the CLK104 board from Xilinx which contains LMK04828B and LMX2594 PLLs to drive clocks int the ZCU208 eval board from Xilinx again. The CLK104 board also has 3 input reference clock options: on board TCXO, SMA input, Recovered clock from FPGA.

I have same problem as in this thread https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1229913/lmk04828-taking-driving_clock-from-another-input-pin-and-i-can-t-figure-out-which-one/4661353#4661353

So, I wanted to use the external reference clock input for the LMK via the CLK104's SMA input and not use the CLK104's on board 10MHz TCXO. I used TICS pro app to only select CLKin0 as the PLL1 input and even if I don't supply any reference clock at SMA input, I still see LMK outputting 500MHz clocks at the outputs (DCLKout0 and 6 as programmed). However the Holdover mode is enabled for LMK (not sure if this has got something to do with)

Any help here is greatly appreciated. Thanks!