Other Parts Discussed in Thread: LMK04821, LMK04832, LMK04616, LMK04610

Consider the case where we wish to synchronize the outputs of two slave LMK04828 devices, both fed by an upstream master LMK04828

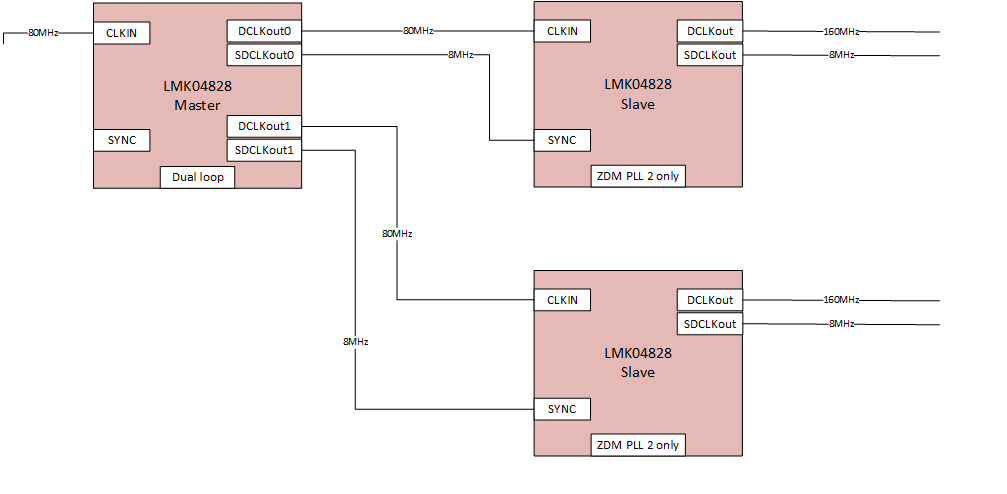

One LMK will act as master, and two will act as slaves. We require matched deterministic phase through each of the paralleled slave LMK04828 devices. The figure below hopefully provides clarification

Some questions

1. With the frequencies shown in the diagram, and the two slave LMK04828s in ZDM PLL2 only config, will the phase through the two slave devices be matched and deterministic?

2. As the 80MHz clock into the slave devices is of course greater than the lowest output clock freq (8MHz Sysref clock), My thought is that I will need to use ZDM with re-clocked divider reset or SYSREF to obtain matched deterministic latency, across the two slave devices. is this correct?

3. Would I be better of providing the slave devices with an 8MHz CLKIN and SYNC, and using the slave devices in Nested 0-delay Dual Loop mode?

Thanks!