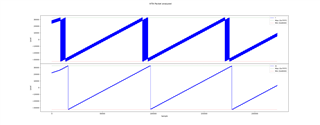

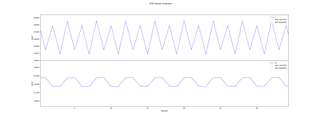

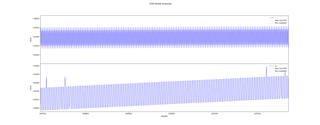

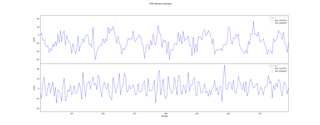

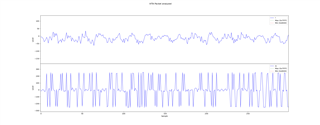

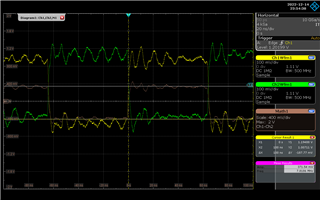

Randomly the chip will either stream data correctly or have the upper bits of the lower byte inverted. Resetting JESD re-randomizes whether or not the issue occurs. On a bad run, the upper 2 bits will randomly become inverted. I believe bit 5 also gets inverted but I'm not 100% sure since the noise floor make it difficult to tell.

Other observations:

- The issue happens on i and q independently

- Using the register to swap the JESD lanes used by LSB and MSB result in the issue following the lane that is now sending the LSB (issue follows the data not the JESD lane)

- Enabling fast OVR results in the lowest byte always being 0 (expected)

- Digital gain of non-zero will affect the DC offset and noise floor but will never result in the noise from the inverted bits entering the MSB (which implies the bit flips are occurring after digital gain)

- Setting a digital gain of 0 results in all data being 0 (which implies the bit flips occur before the digital gain, contradicting the previous point)

- Roughly half the samples in a bad run will be normal, the other have will be affected by this issue

- About a 1/4 chance of this occurring every time JESD is reset

We are using a board we designed. Previous versions of our board did not have this issue, but we can't find any differences in the state of the ADC between this board in the previous ones.