Part Number: DP83869HM

Other Parts Discussed in Thread: TMS570LC4357, DP83869, HALCOGEN, DP83630, DP83640, DP83869EVM

Tool/software:

Hi support team,

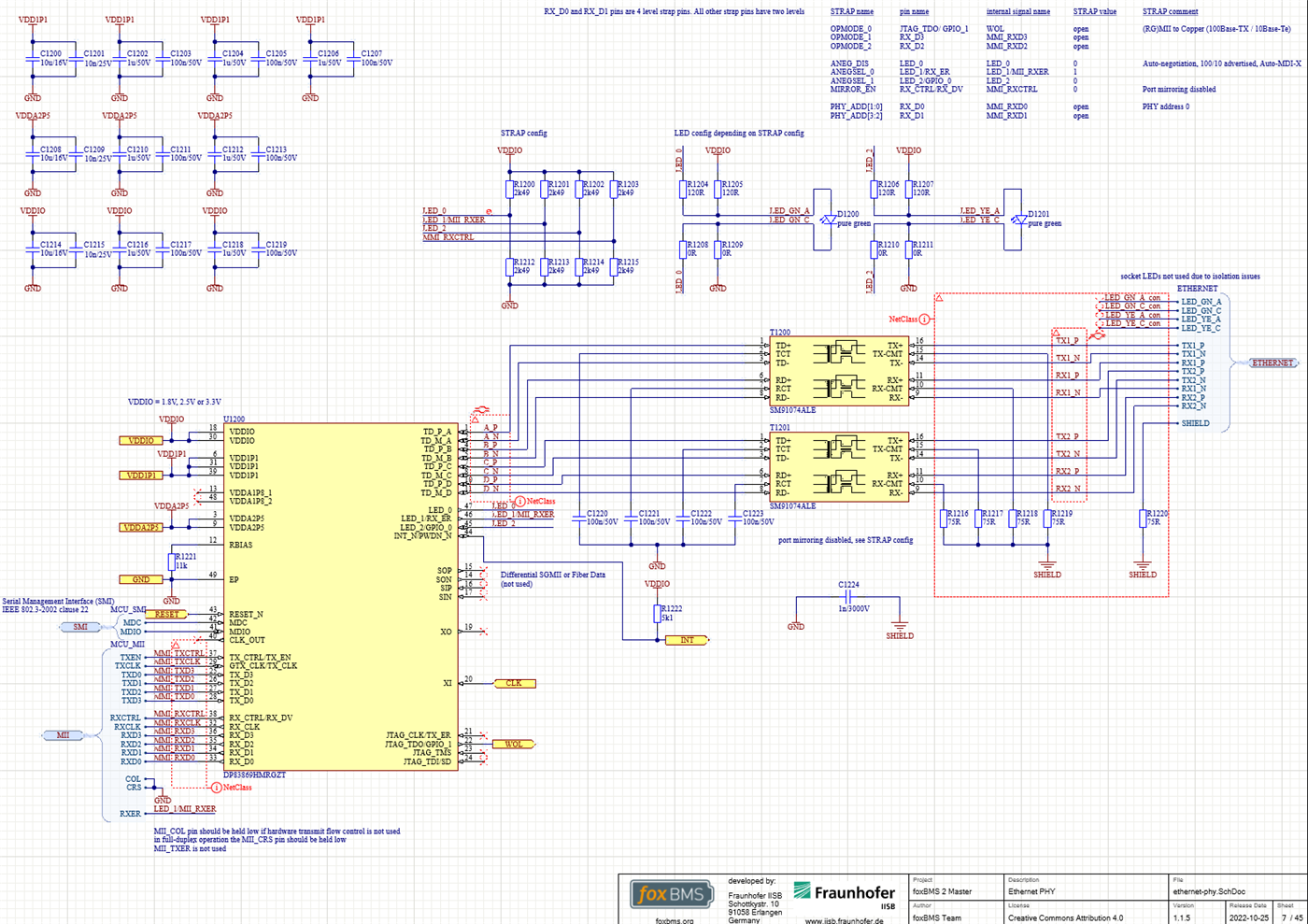

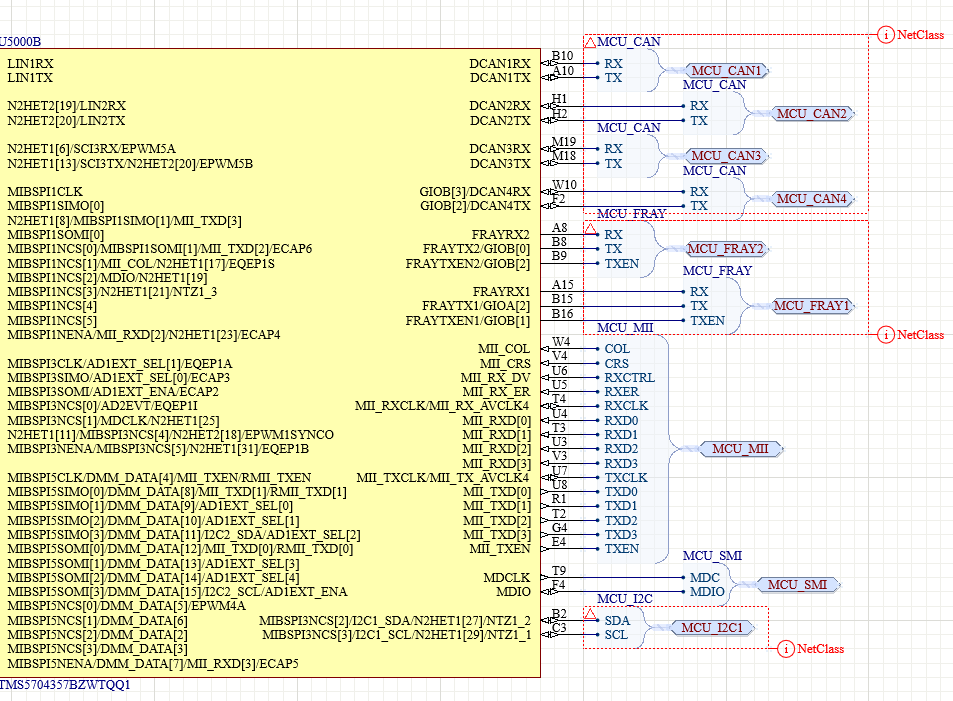

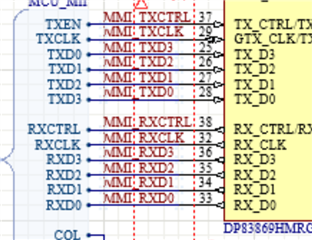

I am trying to integrate the DP83869HM in our FoxBMS (GitHub - foxBMS/foxbms-2: foxBMS 2, online documentation at https://docs.foxbms.org). There we are facing some issues in the MII to copper connection between the PHY and TMS570LC4357. We are not receiving any interrupts on the MAC side in the RXINTSTATRAW register when pinging it via a pc. For the configurationm we are currently using a modified version of the lightweight IP (lwIP) demo (http://git.ti.com/hercules_examples/hercules_examples/trees/master/Application/LwIP)

The MDIO registers show the PHY alive and with link on address 0x00.

The register configuration is as follows:

0x0 BMCR = 0x1140,

0x1 BMSR = 0x796D,

0x2 PHYIDR1 = 0x2000,

0x3 PHYIDR2 = 0xA0F1,

0x4 ANAR = 0x01E1,

0x5 ALNPAR = 0xCDE1,

0x6 ANER = 0x6F,

0x7 ANNPTR = 0x2001,

0x8 ANLNPTR = 0x4006,

0x9 GEN_CFG1 = 0x0,

0xA GEN_STATUS1 = 0x0800,

0xD REGCR = 0x401F,

0xE ADDAR = 0x60,

0xF 1KSCR = 0xF000,

0x10 PHY_CONTROL = 0x5048,

0x11 PHY_STATUS = 0x7C02,

0x12 INTERRUPT_MASK = 0x0,

0x13 INTERRUPT_STATUS = 0x1C42,

0x14 GEN_CFG2 = 0x29C7,

0x15 RX_ERR_CNT = 0x0,

0x16 BIST_CONTROL = 0x0,

0x17 GEN_STATUS2 = 0x40,

0x18 LEDS_CFG1 = 0x6150,

0x19 LEDS_CFG2 = 0x4404,

0x1A LEDS_CFG3 = 0x2,

0x1E GEN_CFG4 = 0x12,

0x1F GEN_CTRL = 0x0

We also do the op mode setting in 0x01DF = 0x0060 and make afterwards the software restart with 0x001F=4000.

Is there anything else we might have missed?

kind regards,

Sven