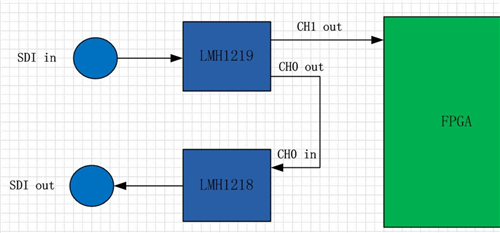

Part Number: LMH1219

Other Parts Discussed in Thread: LMH1218,

Custorm use LMH1219 two outputs: CH1 connect to display, CH0 connect to LMH1218(output by BNC).

When 3G/6G,LMH1219 two outputs are ok.

When 12G, LMH1219 CH1 is ok, CH0 has issue(the output test eye diagram not shown by BNC).

Can give some advise, Thanks!