Other Parts Discussed in Thread: HALCOGEN

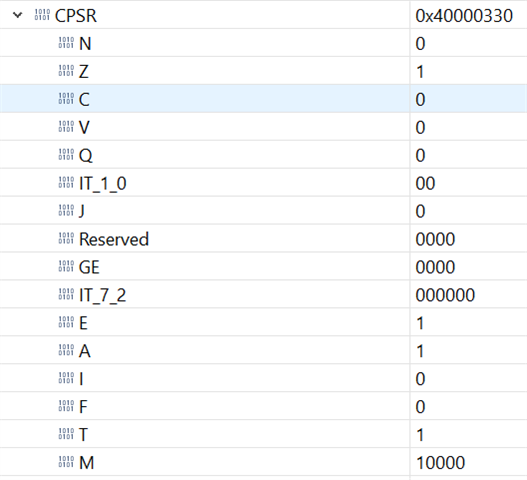

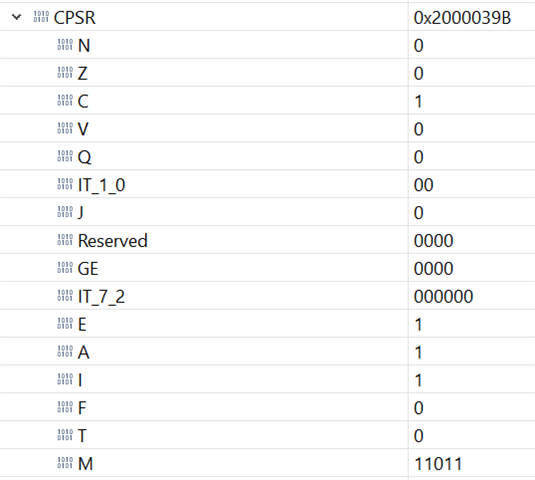

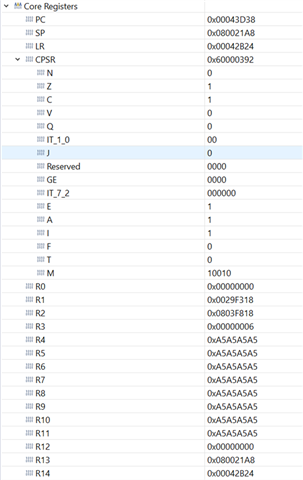

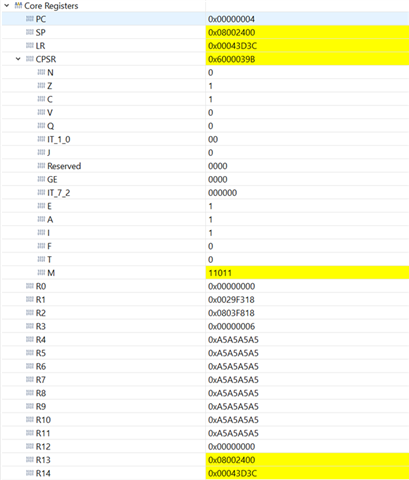

I am currently working on a project and in this project we are using the compile flag "--code_state=16" to compile the project for THUMB instructions. I am running in to an issue where I am entering an IRQ, and upon entering this IRQ the T bit in the CPSR register gets switched from 1 to 0 (THUMB to ARM), but the instructions within this IRQ are still THUMB instructions. Upon executing one of the THUMB instructions (a movs instruction) within the IRQ I get an Undefined Instruction Hard Fault. I am unsure as to whether this is due to trying to execute a THUMB instruction while in ARM mode or if it is because of something else. I have attached an image of the state of the core registers before executing the instruction that causes a hard fault & after the instruction that causes the hard fault. I have also attached a picture of the disassembly of the C code to show exactly what instruction is causing the issue. Any pointers on how to resolve this issue would be greatly appreciated.

Thank you,

Thomas

Before:

After:

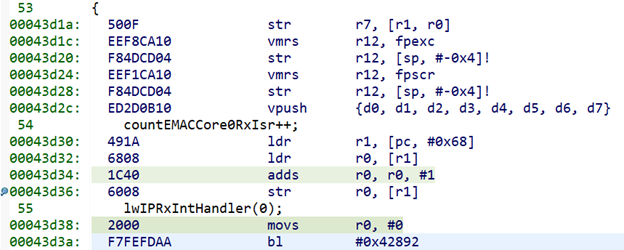

Disassembly: