Other Parts Discussed in Thread: AM2634, SYSCONFIG

Hi

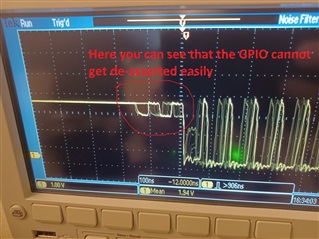

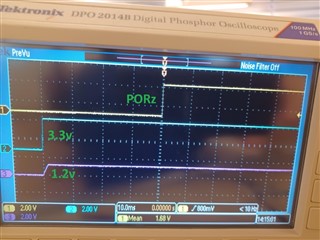

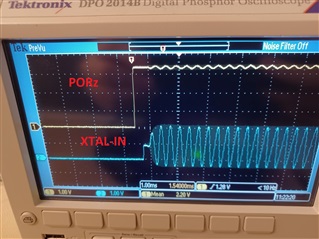

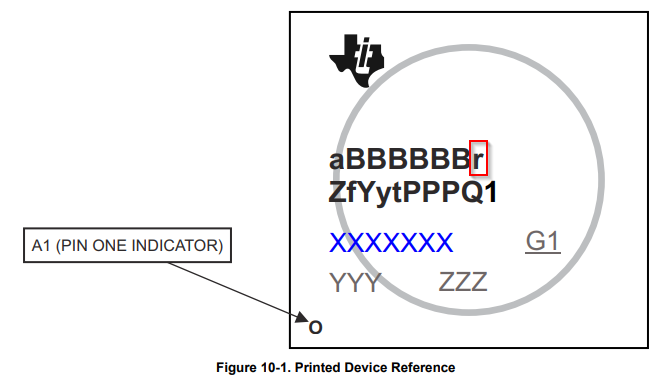

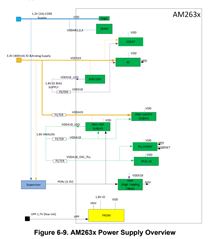

We have designed a MCU(AM2634) +PMIC (TPS653850) board but I am facing a startup issue problem when I add all GPIOs in my final design (about 84 GPIOs) to the "hello world" example code.

Problem Description:

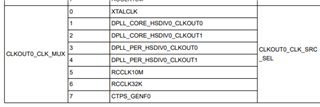

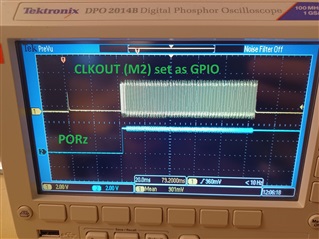

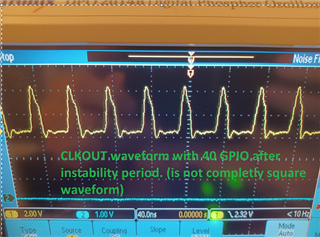

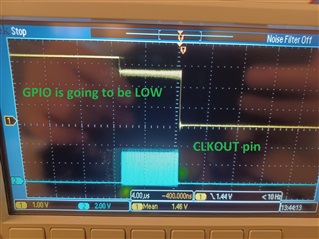

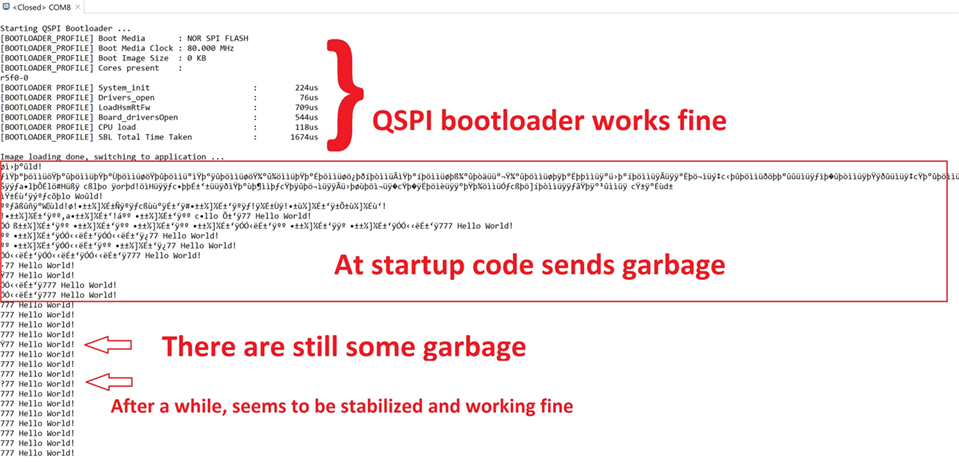

- I have used “hello_world_am263x-cc_r5fss0-0_freertos_ti-arm-clang” example from “AM263x MCU+ SDK 09.00.00” as the base software and added 84 GPIOs to the syscfg file. Only one of these 84 IOs is used as LED and remaining 83 IOs are only initialized in the Sysconfig generated files and never used in the main code.

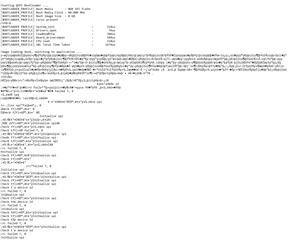

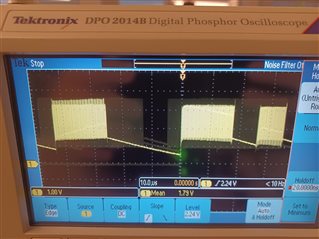

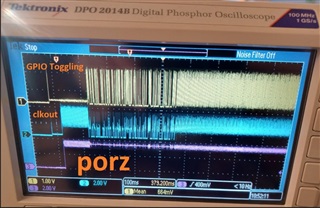

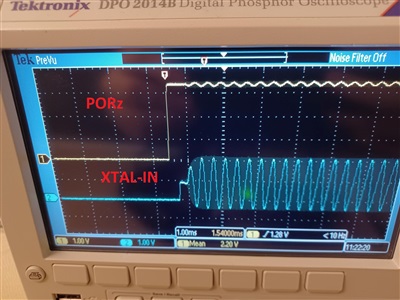

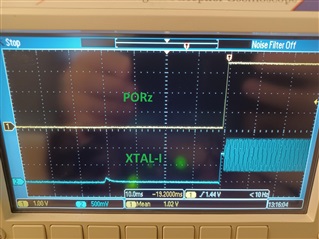

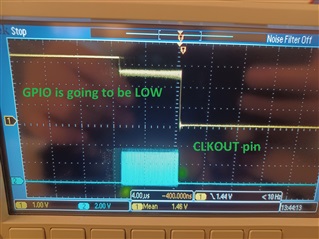

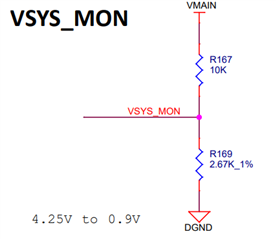

- The problem arises when the board is powered up after being off for a while, the MCU sends garbage to the UART console and it takes time (about 15 seconds) to be fixed and normal data is received on UART. After stablization if the board is turned off and powered up again without significant delay it works fine without problem. Otherwise, if it is off long time the garbages come again.

UART TX data during instability

- The duration of being off has direct relation to the time that the board takes to be stabilized and working fine.

- An important point to mention is that the same code works completely fine in AM263x Control Card EVM.