Other Parts Discussed in Thread: AM3358, , TPS65218D0, TPS65218

Hi,

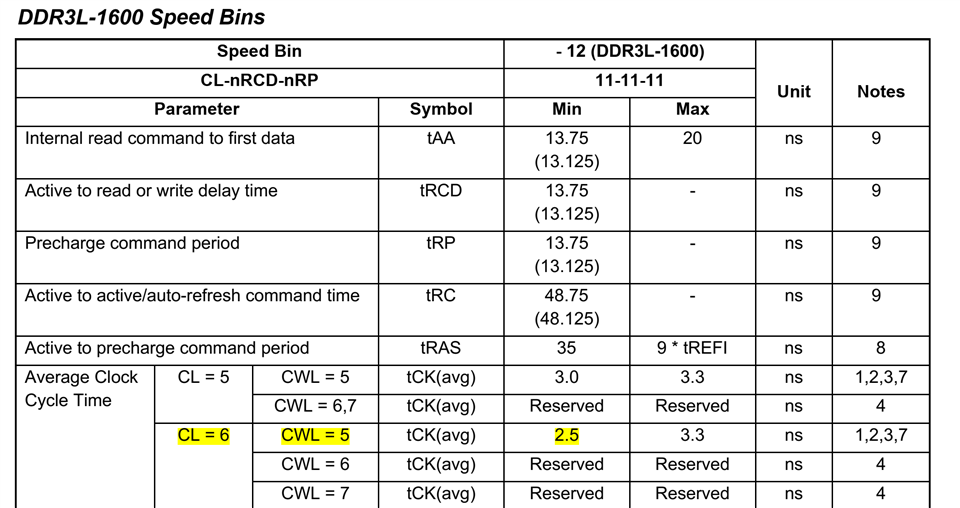

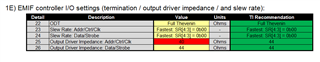

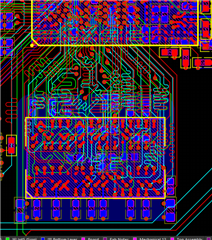

We have a custom board with AM4378 processor and a single AS4C256M16D3LB-12BIN as our DDR. We use single DDR without VTT termination. We have made all the EMIF configurations using EMIF tool. We are running our own Linux image on the board which have been tested in some other design using TI's AM3358. We modified the device tree and kernel settings for the new board and used AM4378EVM as reference too. Attached you can find our DDR schematics and EMIF settings.

The problem we are seeing is that Linux kernel is starting but hangs randomly or stops due to kernel panic during startup at different places but mostly when trying to copy from rootfs. It sometimes goes through and reaches the command line. However 50% of the time it hangs or stops with kernel panic.

We have done memtest at u-boot and did not find any issues however, at times when we can reach command line, we run memorytester and it gives Stuck Address error; FAILURE: possible bad address line at offset XXXXX. (The XXX address changes each time). All other tests of memorytester is OK...When we run the memorytester in a small section (like 256K or 512K) we usually do not see any error but when we do at more than 1MB, we always have the stuck address error.

We need your expertise in this problem. Do you think that this is a memory hardware problem, (ie memory is gone bad) or does it have anything to do with our EMIF or kernel settings?

What do you suggest that we do, to find where the problem is?

Also, please note that in the EMIF tool, we have entered Byte 2 and Byte 3 trace lengths as zero because we are using a single DDR. Can you please confirm this and rest of the EMIF settings please for our setup?

Time is of the essence in this project so you prompt response would be very much appreciated. Thank you!

1108.DDR_Schematic.pdf 8171.SPRAC70A_AM437x_EMIF_Configuration_Tool_V21.xlsx