- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

Hi TI Experts,

I have the below queries regarding the crystal selection.

1. Recommended crystal frequency for MCU_OSC0

2. Do you have recommended part numbers for Crystal?

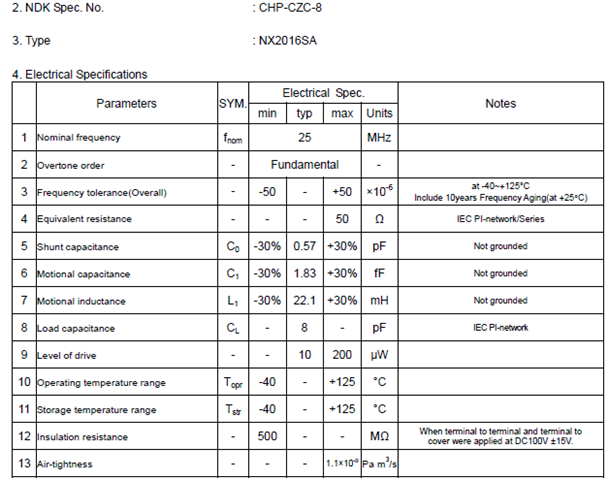

3. Can you help check if NX2016SA-25MHZ-EXS00A-CS10694, CRYSTAL 25.0000MHZ 8PF SMD could be used?

4. Do you have recommendations for MCU_OSC0 crystal selection.

5. Could you share the crystal part number used on the SK-AM62 and SK-AM62-LP?

6. Is it required to always connect the WKUP_LFOSC0?

7. Do you have recommendations for WKUP_LFOSC0 crystal selection.

8. Can i use an oscillator as the clock source?

9. Is there a real max value for crystal ESR?

10. Is there some guidelines for the crystal circuit layout?

11. Is there a delay requirement for the MCU_PORz after all the power supplies ramp and does the delay depend on the clock source

12.Recommended value for Rbias and Rd R

13. MCU_OSC0_XI/MCU_OSC0_OUT starts before VDD_CORE voltage pull high, is this a concern

14. Does it have any side effect when MCU_OSC0_XI clock starts before VDD_CORE voltage pull high? What kind of conditions let MCU_OSC0_XI doesn't start until after VDD_CORE is applied?

15. I would like to check the specifications of the 32kHz XTAL connected to the AM62P.

The following are the specifications of the 25MHz XTAL.

Isn't there a specification for the tolerance range drawn by the green line in the 32kHz XTAL?

Let me know your thoughts.

Hi Board designers,

The FAQ is generic and can also be used for

AM62A7 / AM62A3 / AM62A7-Q1 / AM62A3-Q1 and AM62D-Q1 processor families.

AM62P, AM62P-Q1 processor families

AM62L processor families

Refer below inputs for the queries related to the MCU_OSC0 crystal selection.

1.Recommended crystal frequency for MCU_OSC0

Recommended Crystal Parallel Resonance Frequency for MCU_OSC0 Fxtal is 25 MHz

2. Do you have recommended part numbers for Crystal?

Note that we do not provide part number recommendations.

The system requirements of a customer’s product needs to be considered when selecting a crystal. We do not know the operating conditions or frequency tolerance of all attached devices within their system. The crystal requirements defined in our datasheet only address the processor requirements, but the crystal characteristics may also influence clocks that are sourced to attached devices which have their own requirements. In some cases, the attached devices may have frequency requirements that are tighter than the processor frequency requirements.

3. Can you help check below specs and confirm this crystal specifications meets the requirements for the MCU_OSC0 Internal Oscillator Clock Source.

The device expert and oscillator designer reviewed the crystal requirements and agree this crystal specifications meets the requirements for the HF oscillator implemented on our AM64x, AM62x, AM62Ax, AM62P, AM62P-Q1 Sitara processors.

4. Do you have recommendations for MCU_OSC0 crystal selection.

Refer below sections of the device datasheet.

https://www.ti.com/lit/gpn/am625

Figure 7-16. MCU_OSC0 Crystal Implementation

The crystal must be in the fundamental mode of operation and parallel resonant.

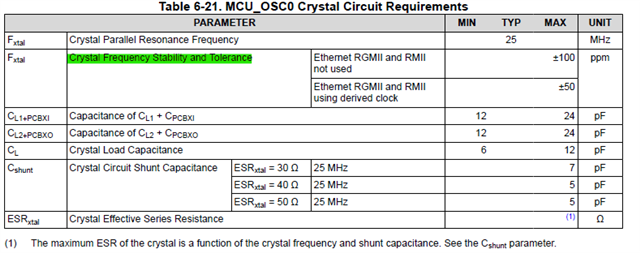

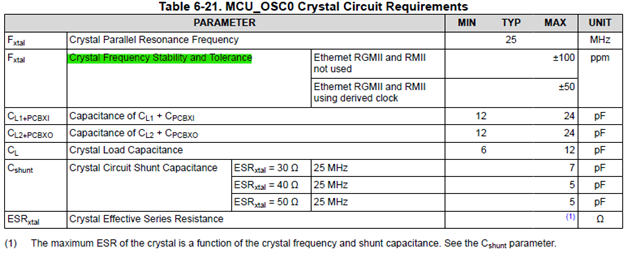

Table 7-19. MCU_OSC0 Crystal Circuit Requirements summarizes the required electrical constraints.

5. Could you share the crystal part number used on the SK-AM62 and SK-AM62-LP?

SK-AM62 and SK-AM62-LP

XRCGB25M000F3M00R0

25 MHz ±30ppm Crystal 6pF 150 Ohms 4-SMD, No Lead

Do consider parasitic capacitance introduced by the PCB when determining the crystal load cap value.

6. Is it required to always connect the WKUP_LFOSC0?

Use of WKUP_LFOSC0 is application dependent.

When WKUP_LFOSC0 is not used refer below section of the datasheet for oscillator connections

7.11.4.1.5 WKUP_LFOSC0 Not Used

Figure 7-25. WKUP_LFOSC0 Not Used - shows the recommended oscillator connections when WKUP_LFOSC0 is not used.

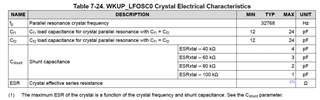

7. Do you have recommendations for WKUP_LFOSC0 crystal selection.

Refer the below section of the device data sheet.

7.11.4.1.2 MCU_OSC0 LVCMOS Digital Clock Source

7.11.4.1.4 WKUP_LFOSC0 LVCMOS Digital Clock Source

Note: Take care of the XO connection as per the data sheet recommendation.

8. Can i use an oscillator as the clock source?

Refer 7.11.4.1.2 MCU_OSC0 LVCMOS Digital Clock Source of the data sheet. Follow the recommended XO termination.

7.11.4.1.4 WKUP_LFOSC0 LVCMOS Digital Clock Source

9. Is there a real max value for crystal ESR?

The maximum ESR recommended is 50 ohms regardless of shunt capacitance.

10. Is there some guidelines for the crystal circuit layout?

We currently have the below guidelines for the AM62A7.

9.3 Clock Routing Guidelines

9.3.1 Oscillator Routing

The Same guidelines can be followed for the AM625 / AM623 / AM625SIP / AM625-Q1 / AM620-Q1

The guidelines will be updated in the next data sheet revision for AM625 / AM623 / AM625SIP / AM625-Q1 / AM620-Q1

11. Is there a delay requirement for the MCU_PORz after all the power supplies ramp and does the delay depend on the clock source

Refer to MCU_PORz Timing Requirements in the device-specific data sheet

RST1 Hold time, MCU_PORz active (low) at Power-up after supplies valid (using external crystal circuit) is 9500000 ns

RST2 Hold time, MCU_PORz active (low) at Power-up after supplies valid and external clock stable (using external LVCMOS clock source) 1200 ns. (This does not include the external oscillator start-up time)

12. Recommended value for Rbias and Rd

WKUP_LFOSC0 Internal Oscillator Clock Source

WKUP_LFOSC0 Crystal Implementation figure shows the recommended crystal circuit. It is recommended that preproduction printed-circuit board

(PCB) designs include the two optional resistors Rbias (500k to 2M ohm) and Rd (0 ohm) in case they are required for proper oscillator operation when combined with production crystal circuit components. In most cases, Rbias is not required and Rd is a 0-Ω resistor. These resistors may be removed from production PCB designs after evaluating oscillator performance with production crystal circuit components installed on preproduction PCBs.

Note: TI does not expect customers to install a Rbias resistor or use any value other than 0 ohms for Rd without contacting TI to discuss any issue they may have with the oscillator.

13. MCU_OSC0_XI/MCU_OSC0_OUT starts before VDD_CORE voltage ramps up, is this a concern

The oscillator is working as expected. It most cases the oscillation will start shortly after its 1.8V power rail is applied, but there may be conditions where it doesn't start until after VDD_CORE is applied.

14. Does it have any side effect when MCU_OSC0_XI clock starts before VDD_CORE voltage ramps up? What kind of conditions let MCU_OSC0_XI doesn't start until after VDD_CORE is applied?

No side effects.

The oscillator has registers in the VDD_CORE power domain that controls some of its operating functions. It is very unlikely the start-up will be delayed until VDD_CORE is valid, but we are being conservative by saying the oscillation will not begin until VDD_CORE is valid to ensure the product designer provides adequate time for the oscillator to start before reset is released.

15. I would like to check the specifications of the 32kHz XTAL.

The following are the specifications of the 25MHz XTAL.

The following are the specifications of the 32KHz XTAL

Isn't there a specification for the tolerance range drawn by the green line in the 32kHz XTAL?

The accuracy of this clock source is primarily a function of your system requirements.

We plan to define a max limit of +/-100PPM for the AM62Px device. However, your specific application may require a more accurate source.

Regards,

Sreenivasa

Hi TI Experts,

I have the below additional queries regarding the crystal selection.

16. It is assumed that when a crystal connected externally has a large change in frequency due to some factor, there will be an effect on the PLL.

I would like to know the effect on the PLL when the frequency changes and how each function will operate. The factors that may cause the frequency to change include initial failure, environment, and manufacturing defects.

17. Does the 25MHz and 32kHz XTAL have an oscillation margin switching function and is there need to configure registers.

18. Do you have some recommendations on the crystal load and load capacitance matching

Let me know your thoughts.

Hi Board designers,

Refer below inputs for the queries related to the MCU_OSC0 crystal selection.

16. It is assumed that when a crystal connected externally has a large change in frequency due to some factor, there will be an effect on the PLL.

I would like to know the effect on the PLL when the frequency changes and how each function will operate. The factors that may cause the frequency to change include initial failure, environment, and manufacturing defects.

Ans: It is not possible for crystals to have a large change in frequency. They have a very high-Q impedance response. The impedance drops dramatically with a very small shift in frequency, which would cause the gain in the oscillator feedback path to drop such that it is not possible to maintain oscillation. So, they are either oscillating at their designed frequency are not oscillating.

17. Does the 25MHz and 32kHz XTAL have an oscillation margin switching function and is there need to configure registers.

No HFOSC0 registers are required to be changed. These registers should remain in their default state.

Select the appropriate crystal circuit components that are compliant to the values defined in the MCU_OSC0 Crystal Circuit Requirements table.

Read the Load Capacitance and Shunt Capacitance sections to select the appropriate crystal circuit components.

The only LFOSC0 register bits that should be changed by the customer are BP_C, PD_C, and CTRLMMR_WKUP_LFXOSC_TRIM[18:16],

where PD_C is reset (0) to enable the oscillator and the BP_C bit is only set (1) to place the oscillator in bypass mode when

using an LVCMOS clock source. The CTRLMMR_WKUP_LFXOSC_TRIM[18:16] bits are set based on the actual capacitance load applied to the crystal,

as defined by the Load Capacitance Equation. The load capacitance range of the crystal will be half of the recommended capacitor value range

since there are connected in series with the crystals resonate circuit.

18. Do you have some recommendations on the crystal load and load capacitance matching

It is recommended to match the crystal load and the load capacitance as per the data sheet recommendations. Any difference in the crystal load and the load cap capacitance selected could result in PPM variation of the clock frequency Choose crystal load as per the standard capacitance availability to ensure matching of the capacitance.

References

Regards,

Sreenivasa

Hi Board designers,

Refer below inputs for AM62A3-Q1: Oscillator Clock Loss Detection. This should be same for all the AM62x devices.

If MCU_PLL_CLKSEL_CLKLOSS_SWTCH_EN is set, when HFOSC0 stops, will it automatically switch to CLK_12M_RC and output to the MCU_ERRORn pin at the same time?

[TI] >> Yes.

Which register can be used to determine that it has been automatically switched to CLK_12M_RC?

[TI] >> You can read ESM event register WKUP_ESM0_ESM_LVL_EVENT_IN_13

Does the oscillator return to HFOSC0 when a warm reset?

[TI] >> I am not sure if I understand this question. When HFOSC0 starts switching again the reference clock will be automatically switched to HFOSC0 clock.

Will it switch to CLK_12M_RC even if HFOSC0 is not oscillating at cold start?

[TI] >> By default MCU_PLL_CLKSEL_CLKLOSS_SWTCH_EN is set to ‘0’. So at cold start, if HFOSC0 is not switching then the mux will not switch to CLK_12M_RC. If HFOSC0 is not switching during cold start, the device will not boot-up.

Regards,

Sreenivasa

Hi Board designers,

Additional references:

https://e2e.ti.com/support/processors-group/processors/f/processors-forum/998892/am3352-crystal-osc0---parameters---esr-and-behaviors

Regards,

Sreenivasa

Hi Board designers,

Additional references:

MCU_OSC0 LVCMOS Digital Clock Source

Regards,

Sreenivasa

Hi Board designers,

Query regarding Spread Spectrum input:

Does MCU_OSC(25MHz) support spread spectrum clock oscillators?

Please refer to the device specific data sheet for the crystal requirement or for using external LVCMOS clock input.

SS clock input is not supported.

Regards,

Sreenivasa

Hi Board designers,

Refer below Digital clock source that has been published.

Refer to device specific data sheet.

Regards,

Sreenivasa