Hi

We are in the process of designing a board with 6678 DSP along with DDR3 interface

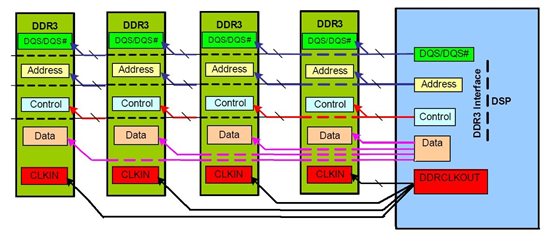

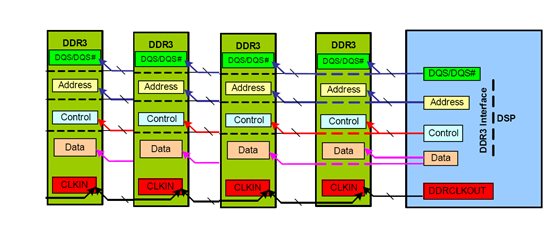

1. Please suggest how to route clock line to the ddr3 chips ..either follow method1 or method2 as attached

2. Also please suggest in the length matching group , clock and address line should be of same length (OR)

clock line length should be greater than address line length by 2 inches....

Method1

Method 2

Thanks