Part Number: AM3352

Dear Champs,

My customer find the high-byte DQS(UDQS) signal was sent before low-byte DQS(LDQS) and thus there was data missing occurred in high-byte.

Is there any way to control UDQS output time to same as LDQS output time?

My customer changed DDR3 memory in their board and found booting fail occurred.

When I checked their board, I found data missing in the high-byte of memory window in the ccs.

The below is my customer's analysis, and they are afraid that there are too many gaps between UDQS time and LDQS time.

* TI AM3352 sends high-byte DQS (UDQS) before low-byte (LDQS) as waveforms check with UDQS and LDQS,

* But WRITE DQS check with M15F1G1664A(2CS), it seems no consecutive DQS running on AM3352, that means booting failed.

* We suppose that data will be missed to strobe during WRITE cycle, if skew is too wide between UDQS and LDQS sent by chipset.

the below is the measurement data. blue line is UDQS and green line is LDQS.

you can find Time gap of 219.26ps at Rising time and 194.14ps at Falling time.

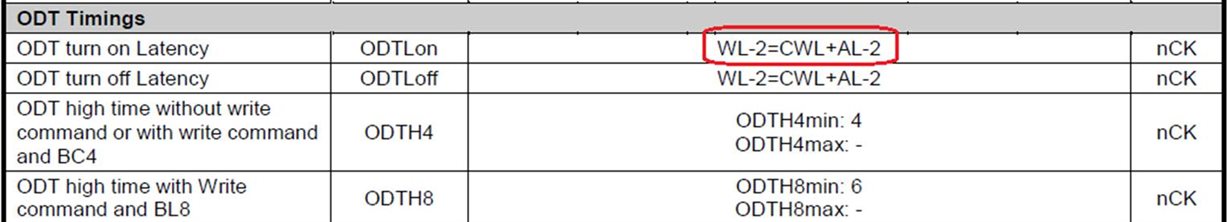

Read tCK(avg): 2.5 ~ 3.3ns, CL=6tCK, Write CWL = 5tCK.

So, if there is a way to control UDQS output time, it would be very helpful.

Thanks and Best Regards,

SI.