Hi Team,

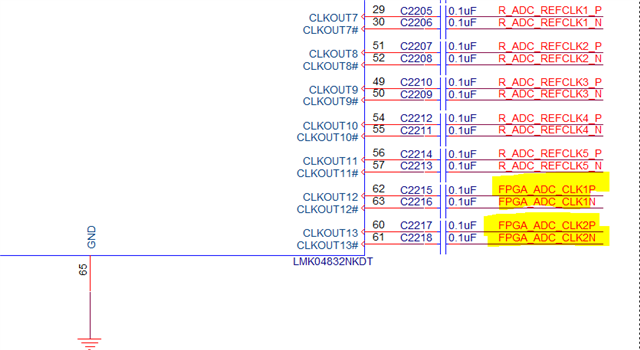

We are using LMK04832NKDT in one of our projects. Please suggest if we can proceed with the below termination approach & values for the LVDS clock outputs.

(Split termination of 100E is used here at the destination side).

(Split termination of 100E is used here at the destination side).

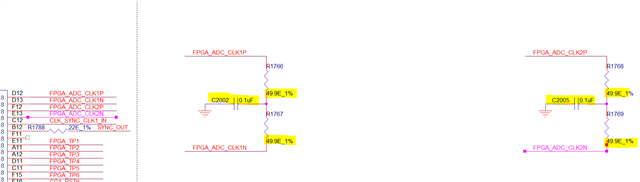

While referring to EVB we found that the capacitors are placed after the termination resistors.

Please suggest if we can place the AC coupling capacitors near the IC itself & the termination (split or single 100E) near the destination.

Or should follow the EVB approach first termination followed by AC coupling capacitor (both at the destination side)?

Please also note that for us the source (LMK) & the destination ICs(FPGA) are placed on separate cards.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.