Other Parts Discussed in Thread: TL431, LM5156

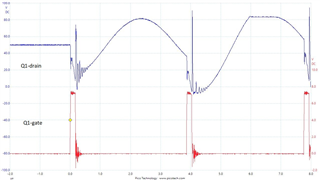

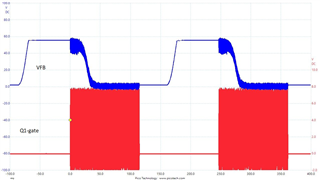

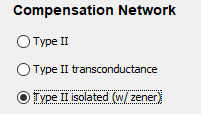

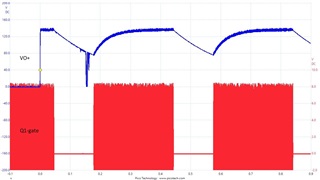

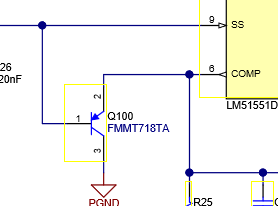

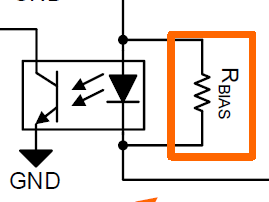

Hello, I am prototyping a 50V to 150V DC flyback converter design. First article of the prototype has been assembled but it is not starting up. I believe the converter is encountering over-current and after the 64 tries during startup, it resets. The controller tries again repeatedly. I have tried various changes as shown by the redline changes in the schematic. I have captured and attached the important waveforms also.

FYI, I also tried changing to 400kHz switching from 250kHz by replacing RT and this resulted in Q1 N-channel FET and T1 failure after a few seconds and the FET getting very hot. I have since replaced the Q1 and T1, and the prototype is back to behaving as previously, i.e. continuously resetting. Please provide your suggestions and remedies.

Kind regards, Denny Wong

Ikomed Technologies