Hi,

Setup

- TDA4VE SOM on EVM boards

- Default Linux + RTOS images from SDK 9.1

- Software uses VPAC, OpenglES, R5F display node, TIDL

- Tivx modification - Default stride set to 64 e2e.ti.com/.../tda4vm-opengl-render-issue-when-migrating-from-sdk-08-02-xx-xx-to-sdk-08-05-xx-xx

Question

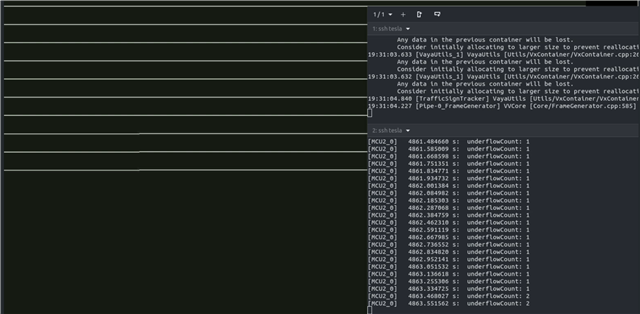

We are currently facing display corruption when using the R5F display node. We use a custom opengl node based on the mosaic one from visionapps and we pass a vximage directly to the display node.

The graph is called in an a vxProcessGraph() and our graph looks like:

inputs -> [opengl openvx node on A72] -> [display node on R5F] -> display port

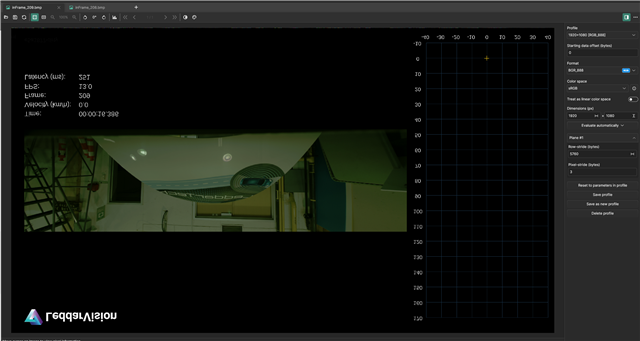

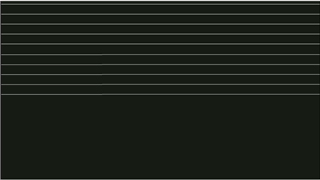

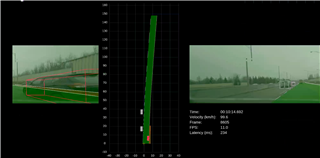

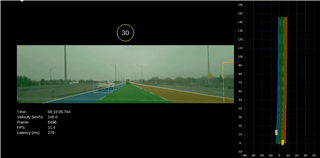

The problem is that at random time (~1/400) we can see corruption in the Y and X axis

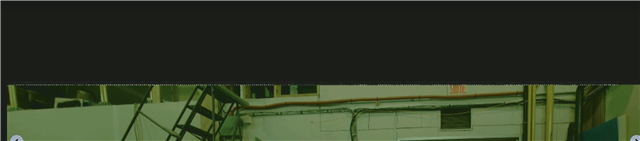

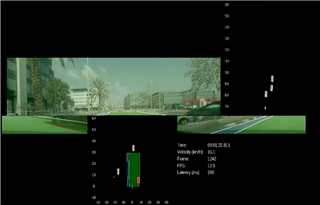

Here a non corrupted image as reference.

Is it a behavior that TI's observed in certain cases or a known issue in the SDK9.1 ?

Thanks,