Part Number: TUSB7320

Other Parts Discussed in Thread: TPS74401

This is a continuation of the question below.

e2e.ti.com/.../tusb7320-cannot-connect-usb-2-0-devices

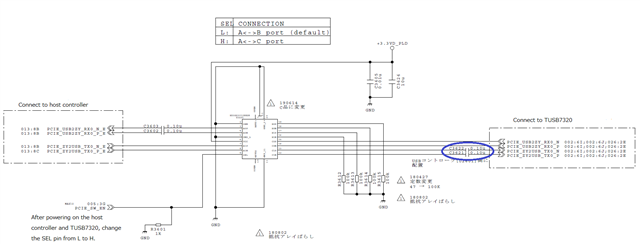

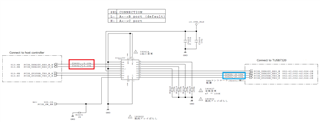

In the third part, the problem that PCIE was not connected with TUSB7320 reoccurred.

I would like to confirm something.

1.

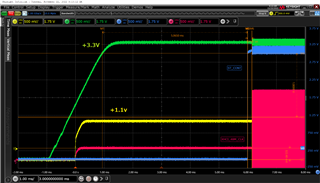

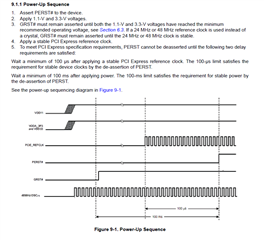

Please check the power supply startup of 3.3V and 1.1V.

Could you please comment on this waveform?

The point of concern is that 1.1V has started up first, but 3.3V has started to rise first.

2.

If PCIE communication is not possible, please tell me how to detect it on the PCIE host side.

I think there are some registers that indicate errors.

3.

Please tell me how to retry when PCIE communication is not possible.

I activated GRST and PERST but it didn't reboot.

Please let me know if there is a signal to reenter other than reset.