Part Number: TMS570LC4357

The CAN module has three message interface registers: IF1, IF2 and IF3. How can I enable DMA to transfer message to IF1 of IF2 data registers and from IF3x data registers?

Part Number: MCU-PLUS-SDK-AM243X

In case of enet_lwip_icssg and enet_lwip_cpsw examples(inclusive of other CPSW and ICSSG examples also):

We see assert when we try to run example again after doing CPU reset in CCS, why is it the case?

I have compiled my CCS projects / MCAL libraries & examples and have binaries with me, how should I be loading or testing them on my board?

Q1 : Does TI devices support hardware accelerators ?

Q2 : What type of supports are present in the hardware ?

Q3. How does application core interact with security core ?

Q4. What are different configuration of devices delivered by TI ?

Q5. What are TI deliverables in software ?

Q6. Is the AutoSAR stack for these drivers available ?

Q7. Will the software delivery also consists of demo examples ?

Q8. What is the cost of the TIFS package ?

Q9. What tools are planned as a part of HSM Care Package ?

In the AM263x IBIS Model.

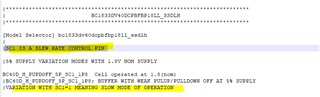

What is the “SC1” feature?

Can it be enabled/disabled in firmware?

Is this is related to silicon binning or some other functionality?

Part Number: AM2634

Am263 supports thermal management of the device by providing control of on-chip temperature sensors.

How to access these sensors to get the SOC temperature?

Part Number: AM2634

Hi, I have gone through the datasheet & TRM of AM2634 for the Dual core and lockstep concept.

I am clear on the concept but to begin with the activities, I'm unsure on how to get this configured or setup to my target HW?

Checked with SysConfig tool as well - no clues found.

Could anyone guide me please on how to get started with the Lockstep mode feature (2 functional cores) & Dual-core mode (4 functional cores) feature to a project separately? Either a special piece of code at the startup or through configurations?

Thanks in Advance.

Regards,

Sharmili Narayanamurthy

Part Number: TMS570LS1224

The PBIST DMA RAM test and PBIST SRAM test pass without any issue. The application is not able to access the SRAM or DMA RAM some times.

Part Number: TMS570LC4357

Part Number: TMS570LS0714

The TRM, datasheet, and HALCOGen don't have PINMUX definition for those two pins. How can I configure pin 39 as N2HET1[21]?