Other Parts Discussed in Thread: TLK10232, CDCM6208

Hi.

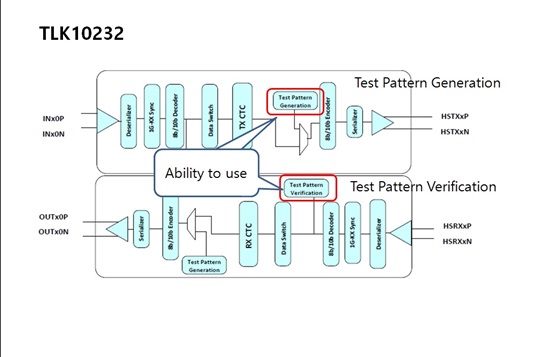

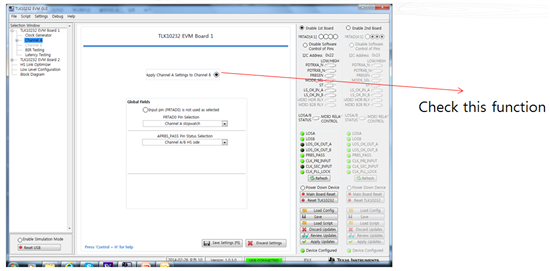

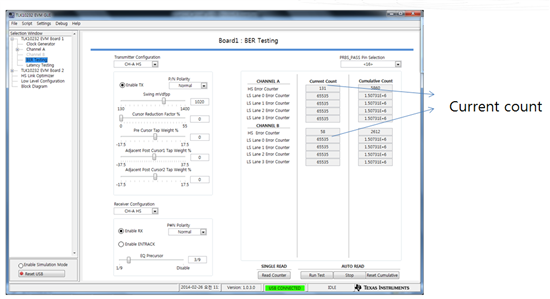

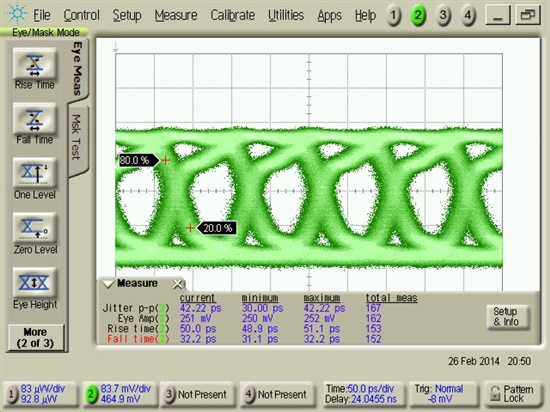

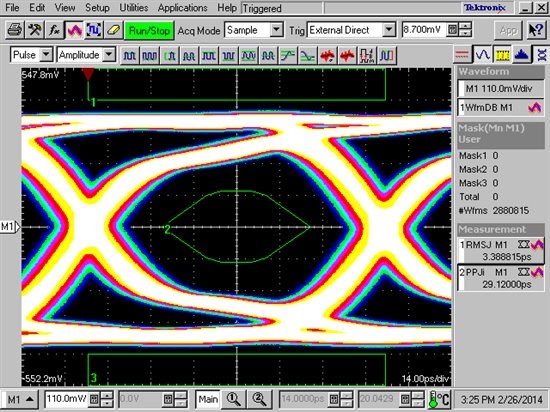

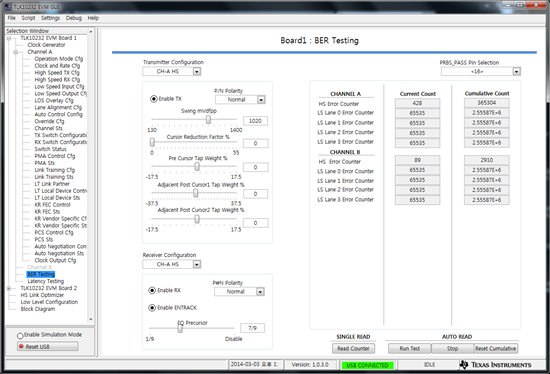

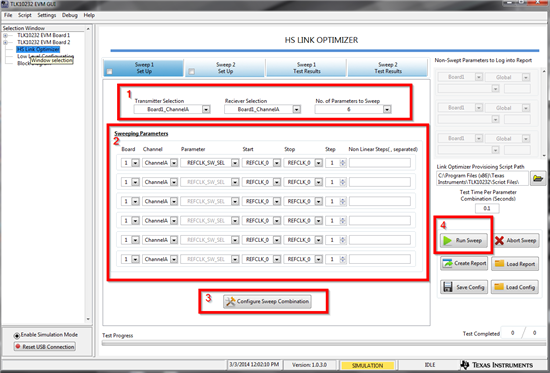

After power is applied to the EVB, (TEST Pattern (PRBS) Generation, TEST Pattern (PRBS) Generation function) BER tests on the steps (procedures) in sequence, tell us, testing in progress, which would help large.

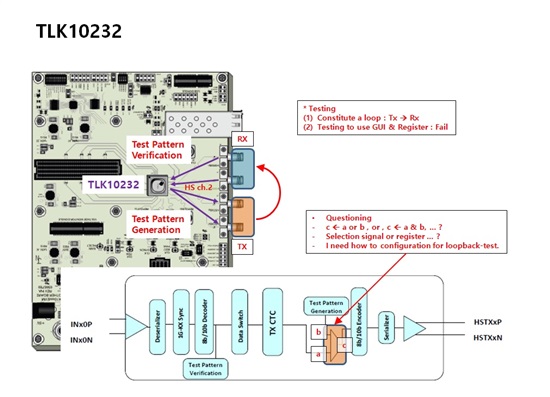

Test Pattern (PRBS) generation & verification test for the optical module functional electrical tests on the Loop, but this behavior has not been confirmed.

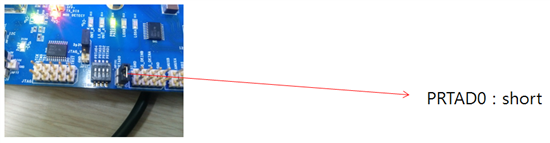

Documentation of test configurations and attached to the questions.