Other Parts Discussed in Thread: AM620-Q1, AM62P, SYSCONFIG, AM625, AM623, AM625-Q1, AM6421, SK-AM62B-P1, AM6442

Tool/software:

Hi TI Experts,

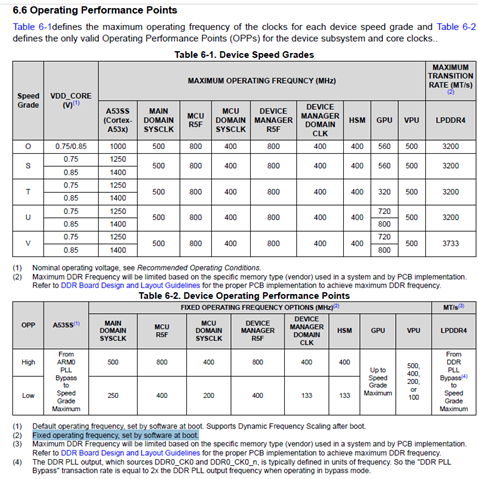

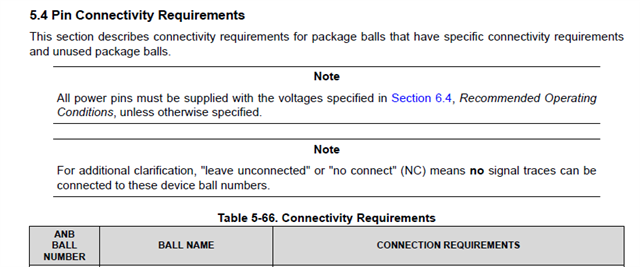

Please share your inputs on processor core, thermal alert, VDD_CORE, VDDR_CORE, VPP and other supplies

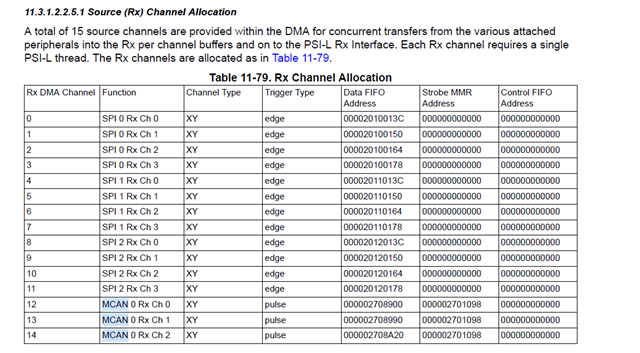

Please share any available information related to the cores that can be used during custom board design