Other Parts Discussed in Thread: TMDS64EVM, SK-AM64B, AM6442, TDA4VM, CDCI6214, TDA4VH, LMK00725, AM6412, DRA821, AM6548, AM67A, AM67, LMK3H0102

Hi TI Experts,

I have the below queries on using the SERDES0 in my design.

1. Supported Interfaces

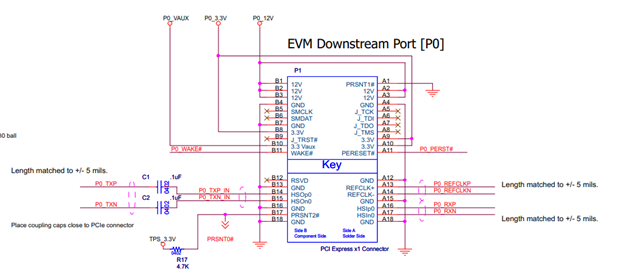

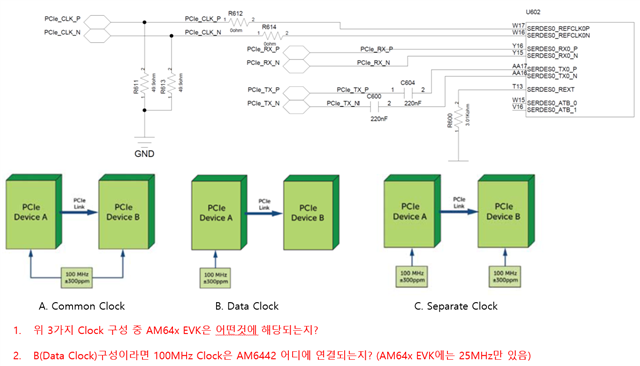

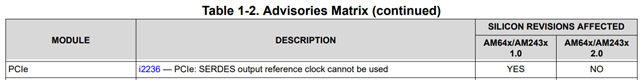

2. Implementation Reference for PCIe

3. Implementation Reference for USB3.0

4. Can i use PCIe and USB3.0 interface at the same time

5. Is AM64 able to change PCIE driving? If yes, how to do?

Let me know your thoughts.

TI references for PCIE

www.ti.com/.../analog-design-journal.html

www.ti.com/.../precision-labs.html

What is PCIe?

www.ti.com/.../6254837397001

www.ti.com/.../interface-pcle-what-is-pcle-presentation-quiz.pdf

www.ti.com/.../retimer_functions_in_pcie_-_slides.pdf

PCIe Link Training Overview

www.ti.com/.../snla415.pdf

KeyStone Architecture Peripheral Component Interconnect Express (PCIe)

www.ti.com/.../sprugs6d.pdf

High-Speed PCB Layout for PCIe Gen 5

www.ti.com/.../snla426.pdf

PCI Express (PCIe) FAQ for KeyStone Devices

www.ti.com/.../sprac59a.pdf

.

.