[FAQ] What TI ESD/TVS diode should I use to protect Interfaces in my system?

[FAQ] What is the difference between TLP and 8/20μs clamping voltages on ESD diode datasheets?

[FAQ] Can an ESD diode experience latch-up?

[FAQ] What capacitance should my ESD diode be?

[FAQ] How do you correlate capacitance needed in ESD protection devices with the protocol data rate?

[FAQ] Device Mismarked with A5

|

|

|

|

|

|

|

|

Power Dissipation and Temperature

|

|

There are many Mux devices in TI high speed portfolio, sometimes it's not easy to select a right part for a particular application.

This FAQ is used to help FAE or customer to choose the right Mux device based on Mux performance, channel numbers, protocols or just a P2P replacement.

Click the links below to navigate to the respective interface FAQs.

Part Number: TUSB2E22

The TUSB2E22, TI's dual eUSB2 to USB repeater, is currently shipping in a small form factor BGA, but what if your application requires an easier to assemble QFN package?

Part Number: TUSB8041

USB 3.0 / 3.1 / 3.2 SuperSpeed 5 Gbps electrical compliance testing requires an oscilloscope and BERT from an approved vendor, as well as dedicated SuperSpeed test fixtures.

Please see the USB-IF website for the most up to date information on equipment and test procedures:

The Electrical Compliance Test Specification for SuperSpeed USB 10 Gbps Rev. 1.0 (February 14, 2017)

The Electrical Compliance Test Specification for SuperSpeed USB Rev. 1.0a (Updated March 30, 2014)

Once the correct equipment and setup are ready, the port under test of the USB 3.x hub will need to enter Compliance Mode for TX testing. Compliance Mode is a state defined by the USB 3.x specification to test the transmitter of the port. Several different test patterns are supported in this mode, with a ping LFPS pattern being sent into the port on the RX lines (typically from a pattern generator) to advance the pattern on the TX lines.

Hub Upstream Port

The upstream port of the hub will transition to Compliance Mode after a Polling LFPS timeout (360 ms) if the port has never successfully completed Polling LFPS after PowerOn Reset. This means that after the hub is powered on and exits reset, if it successfully completes polling (makes a successful USB 3.x connection on the upstream port), then the upstream port will not be able to enter Compliance Mode until the hub is reset or power cycled again. This is to prevent unexpected Compliance Mode entry. A Polling LFPS timeout occurs when the port detects receiver terminations but polling is not successful - this is the case when the upstream port of the hub is connected to the SuperSpeed test setup.

Hub Downstream Ports

In the early versions of the USB 3.x specification, the downstream ports of the hub entered Compliance Mode in the same way as the upstream port. Where if they had not successfully completed Polling LFPS since the last PowerOn Reset, then they would enter Compliance Mode upon a 360 ms Polling LFPS timeout. This is the case for the TUSB8040, TUSB8041 and TUSB8020B hubs. However, due to interoperability issues with unexpected entries to Compliance Mode, this was changed in the later USB 3.1/ USB 3.2 specifications. Please note that the original entry to Compliance Mode on the downstream ports of the hub can be disabled in the TUSB8041 / TUSB8020B devices by setting the dsportEcr_en bit in the hub registers.

It is important to note that the downstream ports of a hub can only enter Compliance Mode if there is a valid SuperSpeed connection on the upstream port of the hub. If there is no upstream SuperSpeed connection, the downstream ports will not be able to enter Compliance Mode. Also the host connected to the upstream port of the hub should be prevented from resetting the downstream ports of the hub during any SuperSpeed compliance testing.

For latest hubs like the TUSB8042 and TUSB8042A, the downstream ports of the hub will only enter Compliance Mode when enabled to do so by a USB command from the host: SetPortFeature(PORT_LINK_STATE) = Compliance Mode. This SuperSpeed command can be generated by the USB IF XHSETT tool: https://usb.org/document-library/xhsett-x64 We recommend using this tool for Compliance Testing since it both generates the necessary command and provides the required SuperSpeed connection on the upstream port of the hub. The tool also prevents unexpected host resets of the downstream ports of the hub while they in compliance mode.

Once the hub port is in Compliance Mode, the TX testing procedure will be dictated by the equipment vendor procedure and the hub should be able to easily support all the necessary test patterns.

Part Number: DS90UB941AS-Q1

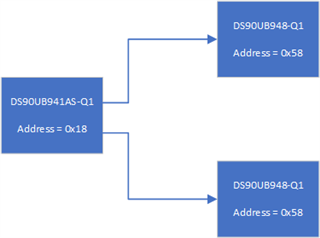

When DS90UB941AS-Q1 is connected to two remote deserializers in splitter or independent mode which have the same physical I2C address, how can they be accessed independently via I2C?

Part Number: DS90UB962-Q1

Hi Team,

I have a build that mixes 960s and 962s due to shortages. One of my cameras that connects to the build needs to dynamically reduce the FPS if it is connected to a 962 because the 3gbps link leads to bandwidth limitations.

Is there a way in software or a register that we can read to tell if the deseralizer we are connected to is a 960 or a 962?

Thanks!

David

Part Number: DS90UB947-Q1

Hi team

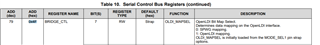

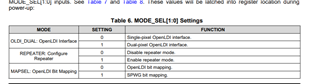

My customer Hasco is using our 947 and configure its mode_sel1, here is our question:

1. When our VR6=0V, the 0x4F read back value is 0x40 which means the bit[7] is 0 and that is described to be the SPWG mapping but in MAPSEL table we see it should be OLDI mapping:

2. When our VR6=0.9V, the 0x4F read back value is 0xC0 which means the bit[7] is 1 and that is described to be the OLDI mapping but in MAPSEL table we see it should be SPWG mapping.

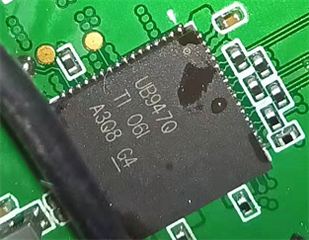

3. Here is our 947 device marking:

Could you please kindly help to review this phenomenon? Thank you.

Part Number: DS90UB954-Q1

In the 954 datasheet the Power Up Sequencing figures 55 and 56 show a hard reset after the first PDB. Is this a requirement, recommendation, or only there to show if you do a hard reset after power up the required timing(t7 and T8)?

If VDD18, VDDIO, and REFCLK are all stable before PDB goes high, is the hard reset still required/recommended?

Thanks,

Justin