Tool/software:

Hello,

I have some problems understanding the fomula for inrush calculation in the TPS1663 eFuse. The datasheet gives two formulas:

(page 16, chapter 9.3.1)

(1) I(inrush) = C(out) x V(in)/tdVdT

(2) tdVdT = 20.8e3…

Tool/software:

Hello,

I have some problems understanding the fomula for inrush calculation in the TPS1663 eFuse. The datasheet gives two formulas:

(page 16, chapter 9.3.1)

(1) I(inrush) = C(out) x V(in)/tdVdT

(2) tdVdT = 20.8e3…

Tool/software:

Hello there,

I am using TLV9004 opamp for one of my application, i am using it as a comparator without any hysteresis

My threshold set in inverting input is 2mV and my signal is ~6mV (for more than…

Tool/software:

Hello,

I am using the unencrypted Pspice model for the OPA2675 in a Cadence Virtuoso testbench. I am trying to drive the gates of two FETs with their own respective op amp, and I like the OPA2675 for its fast slew rate…

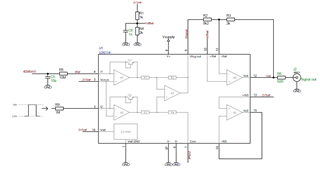

Hi Team,

There is a section I didn't understand in the datasheet 7.3.13.2 describing the maximum slew rate of the automatic ramping must be kept less than 250kHz/us.

The example given 7.3.13.2.2 just below this section shows…

Hello, i have severals questions regarding the LM5069 Reference designs and the Design calculator:

My design uses LM5069 to limit current to approx. 20A @48V and to protect against short circuit. Hot-plug scenarios are not relevant…

To whom it may concern -

Does the SN74LXC8T245-Q1 have an input slew rate requirement (min and max requirement)? If so, what is the requirement?

Thanks,

Brendan

Reducing the slew rate of MAC interface IOs can provide improvement in EMC emissions for some frequencies. This can be done using register 0x456.

0x456 bits [5] and [0] control the impedance of the RX and TX MAC interface pads…

Hi there!! I am about to use the TPS259813ARPWR in one of my new designs and I am a little bit confused about some data of datahseet. It's about the startup calculations and how to check if the startup is safe in my application.…

I am powering the 1.2V VDD/VDDARn rails from an external regulator and need to know if they have any slew rate or ripple requirements.

Your help would be greatly appreciated

Is there any special action required in order to be able to change the function generator slew-rate?

I have test code that successfully sets up the DAC0 output to generate a sine-wave:

// First value (word) is the data, second…

Dear E2E team

I'm evaluating LOG114 for an application that requires some bandwidth.

The test circuit is as follows (Vsupply = 5 V, bypass capacitors not depicted but present):

The measured response is shown in this screenshot…

Hello, It would be really helpful if I learn how was slew rate ( rise and fall times) of the output signal improved, in other words slew rate being increased compared to previous…

Hello everyone!

I am Alper. I am working with GaNFETs with integrated gate driver (LMG3422R030). GaNFET's datasheet states that it has drain to source voltage slew rate during turn on in between 20V/ns - 150V/ns. I designed a…

Hi Team,

I am using THS4032 as a trans-impedance amplifier in one of my applications.

My input signal is a 250kHz, +/-10V signal.

How to calculate the slew rate and gain-bandwidth product required for the op-amp for such a signal.

Actually…

Hi team,

Does THVD1429 have specs of slew rate at A, B bus terminal?

There are no specification so I want to know practical value.

Best regards,

koyo

Noel, thanks again. I did not know about PLL Sim and will check it out.

Effectively, the slew rate is about 6 MHz/us, because the 100 MHz change

is finished after about 16 us.

Noel, thanks for your answer.

So if RAMPx_LEN= 1 (which is not forbidden), with my example the slew rate

(the slope of the frequency ramp) is 10 GHz/us= 10000 MHz/us. Can the

PLL follow this?

For example, in "An Ultra-Wideband Fast Frequency Ramp Synthesizer…

A TI employer answered that the minimum ramp duration is 1/fpd.

Does this mean we get in this small time a nice linear ramp with

a very high frequency slew rate?

E.g., if fpd= 100 MHz and the ramp is from 14 to 14.1 GHz (inside

…